Answered step by step

Verified Expert Solution

Question

1 Approved Answer

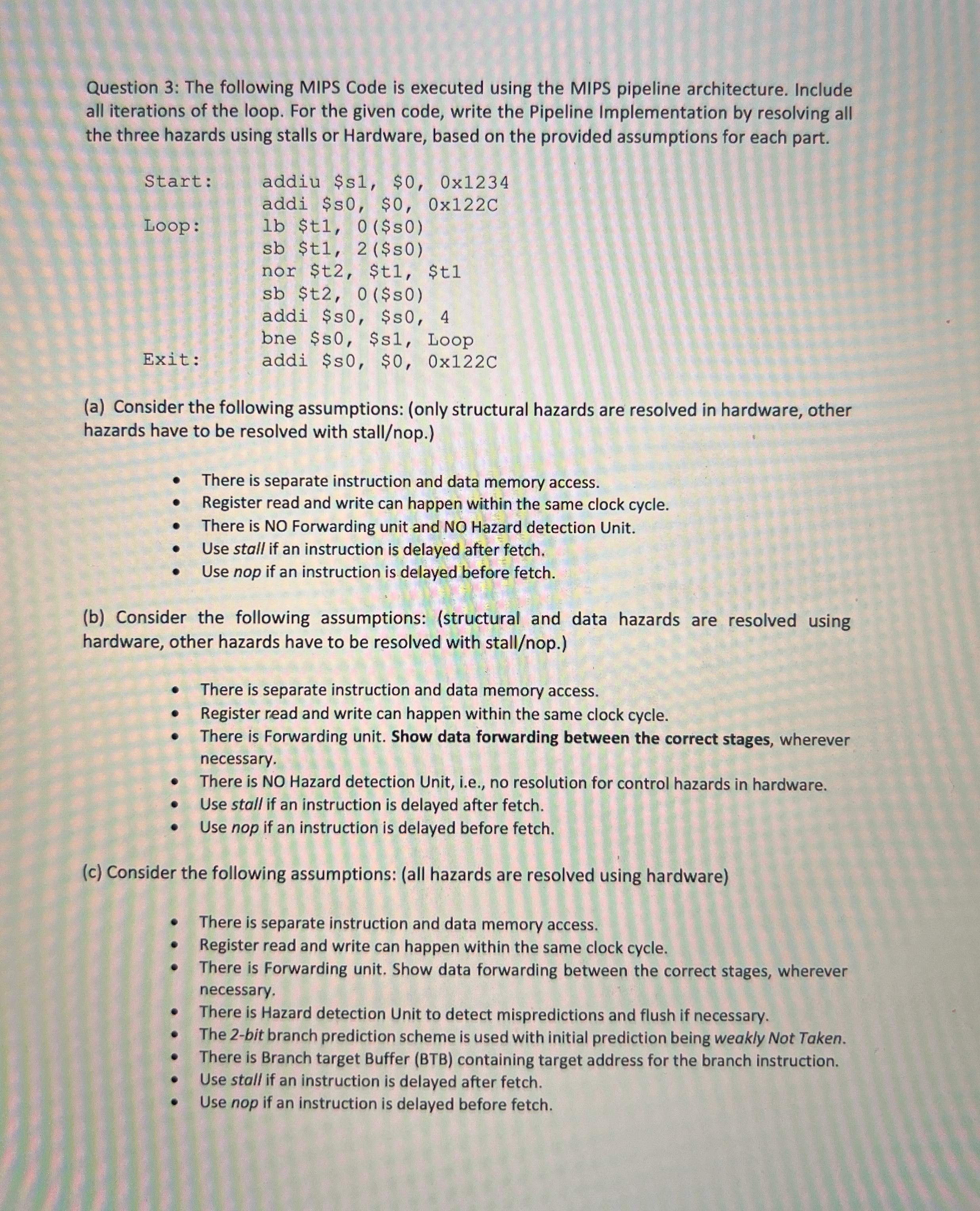

Question 3 : The following MIPS Code is executed using the MIPS pipeline architecture. Include all iterations of the loop. For the given code, write

Question : The following MIPS Code is executed using the MIPS pipeline architecture. Include all iterations of the loop. For the given code, write the Pipeline Implementation by resolving all the three hazards using stalls or Hardware, based on the provided assumptions for each part.

Start: addiu $s $

addi $s $

Loop:

lb $t$

sb $t$

nor $t $t $t

sb $t$

addi $$

bne $$ Loop

Exit: addi $$

a Consider the following assumptions: only structural hazards are resolved in hardware, other hazards have to be resolved with stallnop

There is separate instruction and data memory access.

Register read and write can happen within the same clock cycle.

There is NO Forwarding unit and NO Hazard detection Unit.

Use stall if an instruction is delayed after fetch.

Use nop if an instruction is delayed before fetch.

b Consider the following assumptions: structural and data hazards are resolved using hardware, other hazards have to be resolved with stallnop

There is separate instruction and data memory access.

Register read and write can happen within the same clock cycle.

There is Forwarding unit. Show data forwarding between the correct stages, wherever necessary.

There is NO Hazard detection Unit, ie no resolution for control hazards in hardware.

Use stall if an instruction is delayed after fetch.

Use nop if an instruction is delayed before fetch.

c Consider the following assumptions: all hazards are resolved using hardware

There is separate instruction and data memory access.

Register read and write can happen within the same clock cycle.

There is Forwarding unit. Show data forwarding between the correct stages, wherever necessary.

There is Hazard detection Unit to detect mispredictions and flush if necessary.

The bit branch prediction scheme is used with initial prediction being weakly Not Taken.

There is Branch target Buffer BTB containing target address for the branch instruction.

Use stall if an instruction is delayed after fetch.

Use nop if an instruction is delayed before fetch.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started