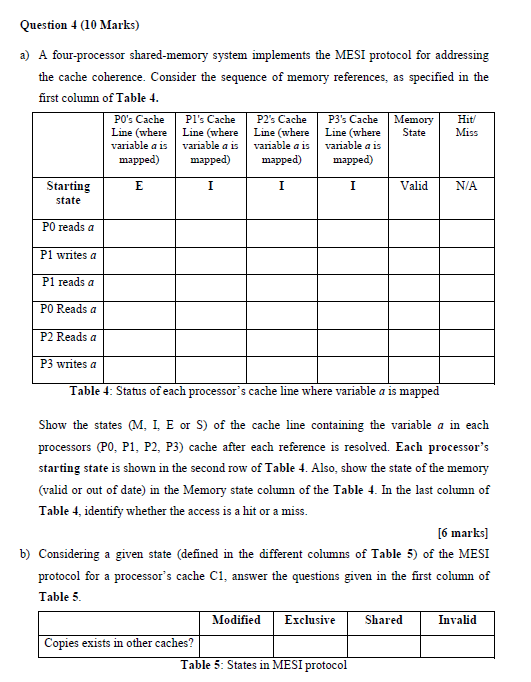

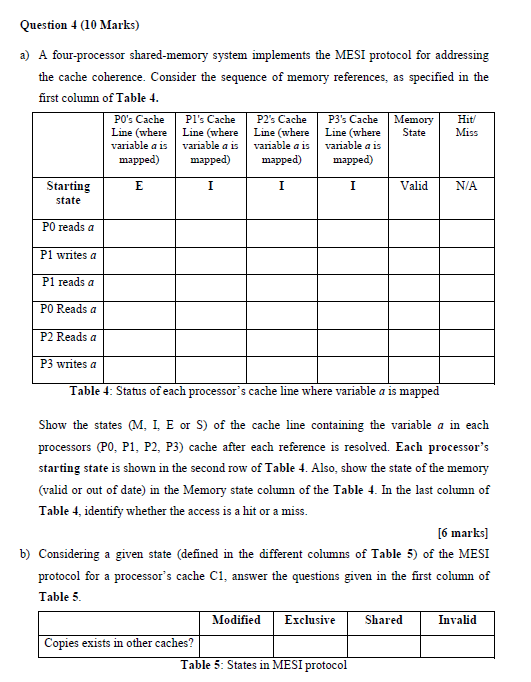

Question 4 (10 Marks) a) A four-processor shared-memory system implements the MESI protocol for addressing the cache coherence. Consider the sequence of memory references, as specified in the first column of Table 4. PO's Cache Pl's Cache P2's Cache P3's Cache Memory Hit Line (where Line (where Line (where Line (where State Miss variable a is variable a is variable a is variable a is mapped) mapped) mapped) mapped) Starting E I I I Valid N/A state PO reads a P1 writes a P1 reads a PO Reads a P2 Reads a P3 writes a Table 4: Status of each processor's cache line where variable a is mapped Show the states M. I. E or S) of the cache line containing the variable a in each processors (PO, P1, P2, P3) cache after each reference is resolved. Each processor's starting state is shown in the second row of Table 4. Also, show the state of the memory (valid or out of date) in the Memory state column of the Table 4. In the last column of Table 4, identify whether the access is a hit or a miss. [6 marks] b) Considering a given state (defined in the different columns of Table 5) of the MESI protocol for a processor's cache C1, answer the questions given in the first column of Table 5. Modified Exclusive Shared Invalid Copies exists in other caches? Table 5: States in MESI protocol Question 4 (10 Marks) a) A four-processor shared-memory system implements the MESI protocol for addressing the cache coherence. Consider the sequence of memory references, as specified in the first column of Table 4. PO's Cache Pl's Cache P2's Cache P3's Cache Memory Hit Line (where Line (where Line (where Line (where State Miss variable a is variable a is variable a is variable a is mapped) mapped) mapped) mapped) Starting E I I I Valid N/A state PO reads a P1 writes a P1 reads a PO Reads a P2 Reads a P3 writes a Table 4: Status of each processor's cache line where variable a is mapped Show the states M. I. E or S) of the cache line containing the variable a in each processors (PO, P1, P2, P3) cache after each reference is resolved. Each processor's starting state is shown in the second row of Table 4. Also, show the state of the memory (valid or out of date) in the Memory state column of the Table 4. In the last column of Table 4, identify whether the access is a hit or a miss. [6 marks] b) Considering a given state (defined in the different columns of Table 5) of the MESI protocol for a processor's cache C1, answer the questions given in the first column of Table 5. Modified Exclusive Shared Invalid Copies exists in other caches? Table 5: States in MESI protocol