Answered step by step

Verified Expert Solution

Question

1 Approved Answer

RISC-V dfAssignment 1 nam.. Assignment 1-7 pdf 4 724 /1665 4.26 This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in

RISC-V

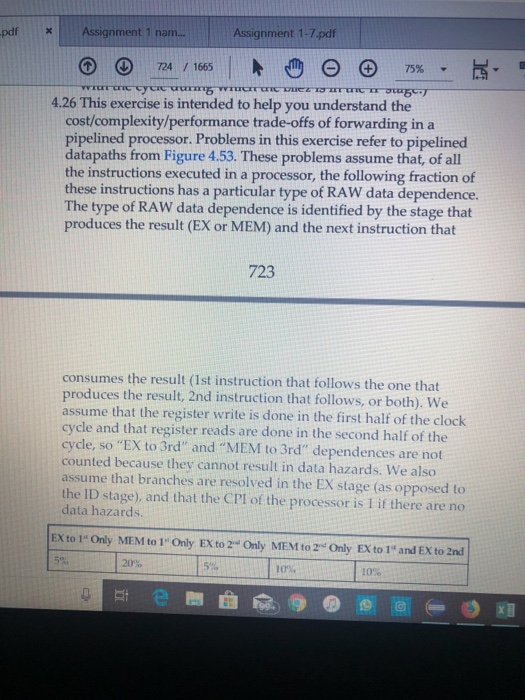

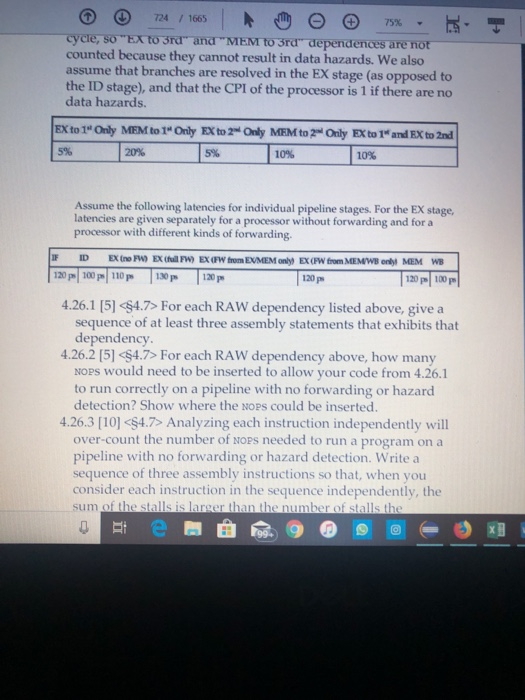

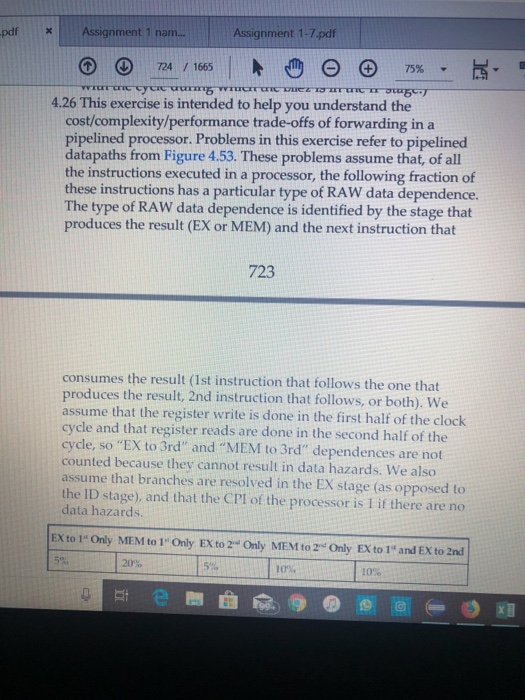

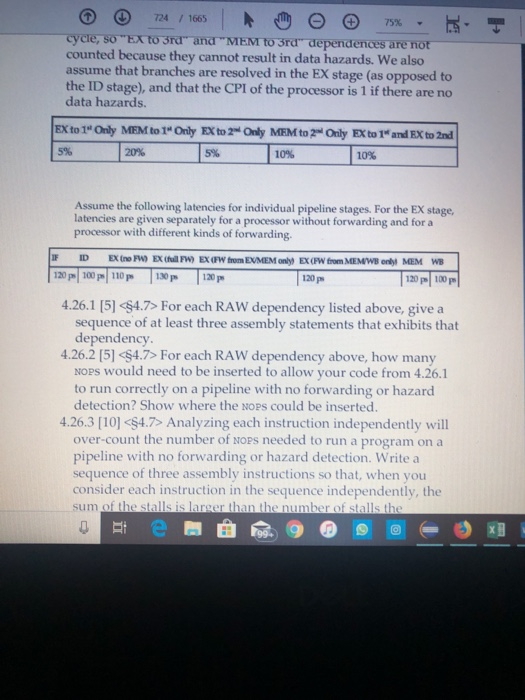

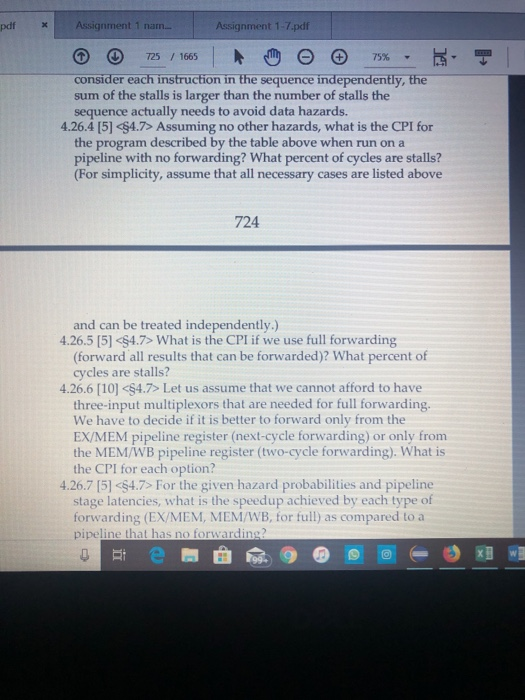

dfAssignment 1 nam.. Assignment 1-7 pdf 4 724 /1665 4.26 This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined datapaths from Figure 4.53. These problems assume that, of all the instructions executed in a processor, the following fraction of these instructions has a particular type of RAW data dependence. The type of RAW data dependence is identified by the stage that produces the result (EX or MEM) and the next instruction that 723 consumes the result (1st instruction that follows the one that produces the result, 2nd instruction that follows, or both). We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle, so "EX to 3rd" and "MEM to 3rd" dependences are not counted because they cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards. EX to 1 Only MEM to 1 Only EX to 2 Only MEM to 2 Only EX to 1 and EX to 2nd 5% 10% 10% 724 1665 75% to 3ra dependences are not counted because they cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards. 15% 120% '15% '110% -110% Assume the following latencies for individual pipeline stages. For the EX stage, latencies are given separately for a processor without forwarding and for a processor with different kinds of forwarding. 120 p 100p 110p 130p 120p 4.26.1 [5] For each RAW dependency listed above, givea 4.26.2 (5] For each RAW dependency above, how many 120 ps 120 p 100 p sequence of at least three assembly statements that exhibits that dependency NoPs would need to be inserted to allow your code from 4.26.1 to run correctly on a pipeline with no forwarding or hazard detection? Show where the NOPs could be inserted. 4.26.3 [10] Analyzing each instruction independently will over-count the number of Nops needed to run a program on a pipeline with no forwarding or hazard detection. Write a sequence of three assembly instructions so that, when you consider each instruction in the sequence independently, the sum of the stalls is r than the number of stalls th pdfAssignment 1 nam Assignment 1-7.pdf 0 725 1665 consider each instruction in the sequence in sum of the stalls is larger than the number of stalls the sequence actually needs to avoid data hazards. dependently, the 4.26.4 [5] Assuming no other hazards, what is the CPI for the program described by the table above when run on a pipeline with no forwarding? What percent of cycles are stalls? (For simplicity, assume that all necessary cases are listed above 724 and can be treated independently.) 4.26.5 [5] What is the CPI if we use full forwarding (forward all results that can be forwarded)? What percent of cycles are stalls? 4.26.6 [10] Let us assume that we cannot afford to have three-input multiplexors that are needed for full forwarding. We have to decide if it is better to forward only from the EX/MEM pipeline register (next-cycle forwarding) or only from the MEM/WB pipeline register (two-cycle forwarding). What is the CPI for each option? 4.26.7 [5] For the given hazard probabilities and pipeline stage latencies, what is the speedup achieved by each type of forwarding (EX/MEM, MEM/WB, for full) as compared to a ne that has no forwarding dfAssignment 1 nam.. Assignment 1-7 pdf 4 724 /1665 4.26 This exercise is intended to help you understand the cost/complexity/performance trade-offs of forwarding in a pipelined processor. Problems in this exercise refer to pipelined datapaths from Figure 4.53. These problems assume that, of all the instructions executed in a processor, the following fraction of these instructions has a particular type of RAW data dependence. The type of RAW data dependence is identified by the stage that produces the result (EX or MEM) and the next instruction that 723 consumes the result (1st instruction that follows the one that produces the result, 2nd instruction that follows, or both). We assume that the register write is done in the first half of the clock cycle and that register reads are done in the second half of the cycle, so "EX to 3rd" and "MEM to 3rd" dependences are not counted because they cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards. EX to 1 Only MEM to 1 Only EX to 2 Only MEM to 2 Only EX to 1 and EX to 2nd 5% 10% 10% 724 1665 75% to 3ra dependences are not counted because they cannot result in data hazards. We also assume that branches are resolved in the EX stage (as opposed to the ID stage), and that the CPI of the processor is 1 if there are no data hazards. 15% 120% '15% '110% -110% Assume the following latencies for individual pipeline stages. For the EX stage, latencies are given separately for a processor without forwarding and for a processor with different kinds of forwarding. 120 p 100p 110p 130p 120p 4.26.1 [5] For each RAW dependency listed above, givea 4.26.2 (5] For each RAW dependency above, how many 120 ps 120 p 100 p sequence of at least three assembly statements that exhibits that dependency NoPs would need to be inserted to allow your code from 4.26.1 to run correctly on a pipeline with no forwarding or hazard detection? Show where the NOPs could be inserted. 4.26.3 [10] Analyzing each instruction independently will over-count the number of Nops needed to run a program on a pipeline with no forwarding or hazard detection. Write a sequence of three assembly instructions so that, when you consider each instruction in the sequence independently, the sum of the stalls is r than the number of stalls th pdfAssignment 1 nam Assignment 1-7.pdf 0 725 1665 consider each instruction in the sequence in sum of the stalls is larger than the number of stalls the sequence actually needs to avoid data hazards. dependently, the 4.26.4 [5] Assuming no other hazards, what is the CPI for the program described by the table above when run on a pipeline with no forwarding? What percent of cycles are stalls? (For simplicity, assume that all necessary cases are listed above 724 and can be treated independently.) 4.26.5 [5] What is the CPI if we use full forwarding (forward all results that can be forwarded)? What percent of cycles are stalls? 4.26.6 [10] Let us assume that we cannot afford to have three-input multiplexors that are needed for full forwarding. We have to decide if it is better to forward only from the EX/MEM pipeline register (next-cycle forwarding) or only from the MEM/WB pipeline register (two-cycle forwarding). What is the CPI for each option? 4.26.7 [5] For the given hazard probabilities and pipeline stage latencies, what is the speedup achieved by each type of forwarding (EX/MEM, MEM/WB, for full) as compared to a ne that has no forwarding

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started