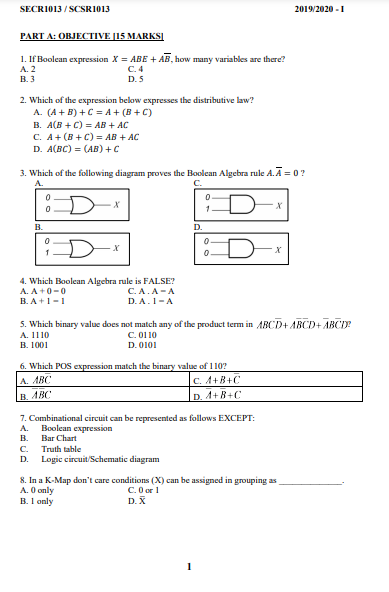

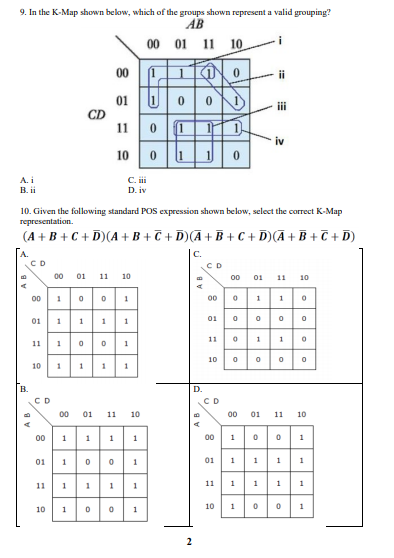

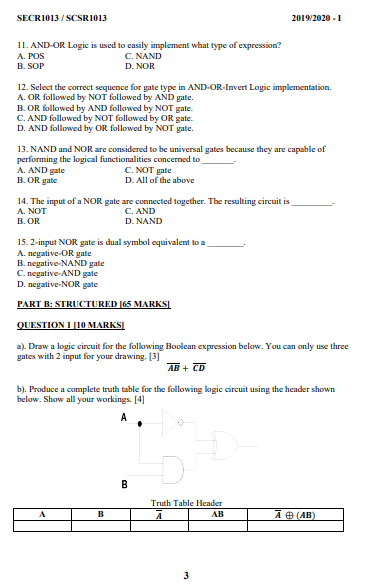

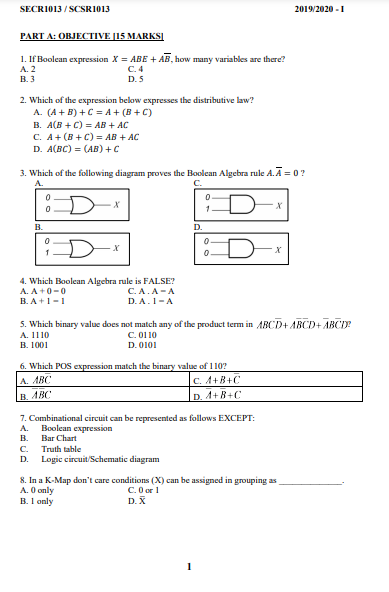

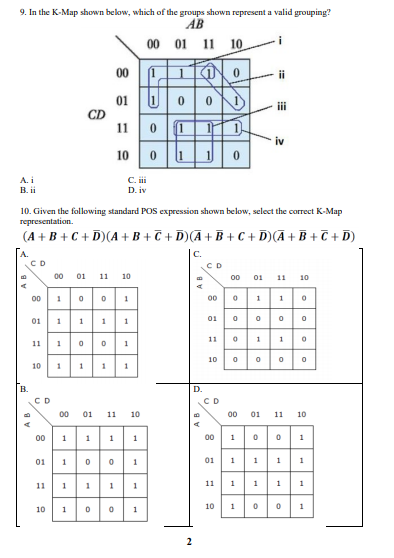

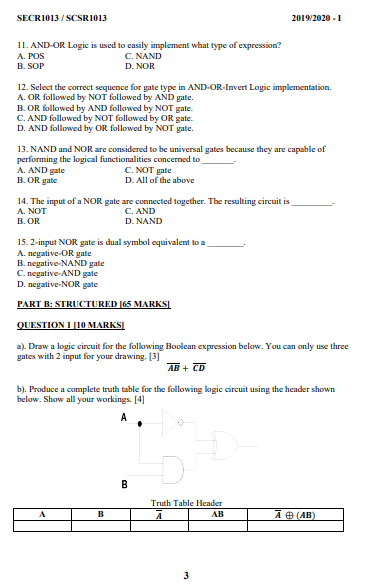

SECR1013/SCSR1013 2019/2020 - 1 PART A: OBJECTIVE [15 MARKS 1. If Boolean expression X = ABE + AB, how many variables are there? A. 2 B DS 2. Which of the expression below expresses the distributive law? A. (A+B) +C = A + (B+C) B. A(B+C) = AB + AC C. A+(B+C) = AB + AC D. ABC) = (AB) + C 3. Which of the following diagram proves the Boolean Algebra rule A. =0? C. 0 0 0 D B. D iD- 0 0 4. Which Boolean Algebra rule is FALSE? A. A +0-0 C.A.A-A B. A+ 1-1 D.A.I-A 5. Which binary value does not match any of the product term in ARCD+ABCD+ABCI A. 1110 C. 0110 B. 1001 D. 0101 6. Which POS expression match the binary value of 110? A ABC C. A+B+C D4+B+C 7. Combinational circuit can be represented as follows EXCEPT: A. Boolean expression Bar Chart C. Truth table D. Logic circuit/Schematic diagram 8. In a K-Map don't care conditions (X) can be assigned in grouping as A. O only C.0 or 1 B. I only D.X 1 9. In the K-Map shown below, which of the groups shown represent a valid grouping? AB 00 01 11 10 i 000 100 ii iii 01 00N CD 11 0 1 100 1 0 iv A. I B. ii D. iv representation. 10. Given the following standard POS expression shown below, select the correct K-Map (A+B+C+DA+B+C+DA+B+C+DA+B+C+D C. A. CD 00 01 11 10 00 01 10 00 10 0 1 0 01 1 01 o 0 o o 11 11 0 0 10 0 1 10 0 o 0 0 10 1 1 1 1 B. D CD CD 00 01 11 10 00 0111 10 AB AB 00 1 1 1 1 00 1 0 0 1 01 1 0 0 1 01 1 1 1 1 11 1 1 11 1 1 10 1 10 0 D 1 1 0 0 1 2 SECR1013 / SCSR1013 2019/2020- 11. AND-OR Logic is used to easily implement what type of expression? A. POS C. NAND B. SOP D. NOR 12. Select the correct sequence for gate type in AND-OR-Invert Logic implementation. A. OR followed by NOT followed by AND gate. B. OR followed by AND followed by NOT gate. C. AND followed by NOT followed by OR gate. D. AND followed by OR followed by NOT gate. 13. NAND and NOR are considered to be universal gates because they are capable of performing the logical functionalities concerned to A. AND gate C. NOT gate B. OR gate D. All of the above 14. The input of a NOR gate are connected together. The resulting circuit is A. NOT C. AND B.OR D. NAND 15.2-input NOR gate is dual symbol equivalent to a A. negative OR gate B. negative-NAND gate C. negative-AND gate D. negative-NOR gate PART B: STRUCTURED 65 MARKS QUESTION 110 MARKSI a). Draw a logic circuit for the following Boolean expression below. You can only use three gates with 2 input for your drawing. [3] AB + CD b). Produce a complete truth table for the following logic circuit using the header shown below. Show all your workings (4) B Truth Table Header AB B (AB) 3 SECR1013 / SCSR1013 2019/2020 - 1 c). Draw timing diagram for output X = A B in your answer booklet. Please copy and redraw the timing diagram exactly as shown below in your answer booklet. [31 A B QUESTION 2 17 MARKSI a). Specify the correct gate for iv for the following statements: (2.5) Gate Statement A HIGH output occurs only when all three inputs are LOW. A LOW output occurs only when any of the inputs is LOW. A LOW output occurs only when all eight inputs are HIGH. A LOW output occurs when the inputs are the same. A HIGH output occurs when any of one input is HIGH or both inputs are HIGH Hii iv v b). Draw the circuit using 2 input basic gates only (AND, OR, NOT) to implement Boolean expression X = [D+ (A+B)C] E [4.5] QUESTION 3 [10 MARKS a). Simplify Boolean expression Z = (A + B)(A + B) using Boolean Algebra laws and rules. Show all your workings. [4] b). Using DeMorgan's theorem, simplify the following Boolean expressions. Show all your workings. [6] i. Y = A(B+C)D ii. S = A + B + CD SECR1013 / SCSR1013 2019/2020- QUESTION 4|13 MARKS] a). From Boolean expression S (A + B)C[4 i. Create and complete the truth table using the following header shown below. Show all your workings. A S ii. Get standard SOP form from the truth table above. b). For Boolean expression X = ABCD+CD+AC + D, produce SOP simplified expression using K-Map minimization Show all your workings. [5] c). Using K-Map minimization, find POS expression for the following. Show all your workings. [4 W - Aco (0,5,10,13) + d(2,7,8, 15) QUESTION SIZ MARKSI a). Convert the logic circuit below to 2 input NOR universal gate only. Show all your workings. [3] b). Convert and simplify the NAND only circuit below to 2 input basic gates (AND, OR, NOT). Show all your workings.[4] DD boo 5 SECR1013 / SCSR1013 2019/2020 - QUESTION 618 MARKS A1 Design a combinational circuit that implements and analyze the following functions: [18] Multiply OUTI Compare Circuit EQ AD OUTO B1 BO Function Multiply Multiply two decimals 2 bit numbers A1A0 and BIBO. Rules: OUTIOUTO is multiplication result between two decimals numbers in binary. OUTIOUTO is INVALID if multiplication result between two decimals numbers in binary is LARGER than 3. Function Compare Compare two decimals 2 bit numbers A1AO and BIBO Rules: EQ set to HIGH if the two decimal numbers are equal EQ set to LOW if the two decimal numbers are different a). Using the following header, create the truth table for the combinational circuit. INPUT OUTPUT AI AO BI OUTI OUTO EQ b). From the truth table above, get the simplified SOP expression for OUT1, OUTO and EQ using K-Map minimization. c). Draw circuit for OUT1 using 2 input basic gates only (AND, OR). d). Draw circuit for OUTO using 2 input basic gate only (AND). e). Draw circuit for EQ using 4 input basic gates only (AND, OR, NOT)