Answered step by step

Verified Expert Solution

Question

1 Approved Answer

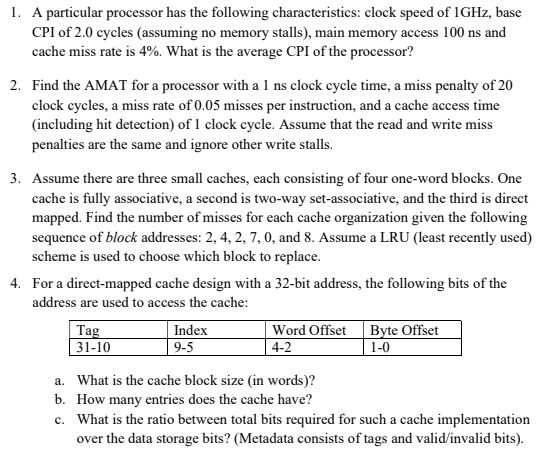

Solve ALL the following exercises. Thank you in advance. 1. A particular processor has the following characteristics: clock speed of 1GHz, base CPI of 2.0

Solve ALL the following exercises.

Thank you in advance.

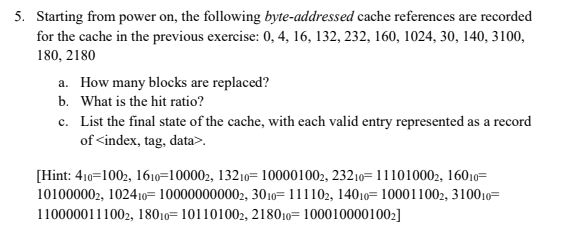

1. A particular processor has the following characteristics: clock speed of 1GHz, base CPI of 2.0 cycles (assuming no memory stalls), main memory access 100 ns and cache miss rate is 4%. What is the average CPI of the processor? 2. Find the AMAT for a processor with a l ns clock cycle time, a miss penalty of 20 clock cycles, a miss rate of 0.05 misses per instruction, and a cache access time (including hit detection) of I clock cycle. Assume that the read and write miss penalties are the same and ignore other write stalls. 3. Assume there are three small caches, each consisting of four one-word blocks. One cache is fully associative, a second is two-way set-associative, and the third is direct mapped. Find the number of misses for each cache organization given the following sequence of block addresses: 2, 4, 2, 7, 0, and 8. Assume a LRU (least recently used) scheme is used to choose which block to replace. 4. For a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache: Tag Index Word Offset Byte Offset 31-10 9-5 4-2 1-0 a. What is the cache block size (in words)? b. How many entries does the cache have? c. What is the ratio between total bits required for such a cache implementation over the data storage bits? (Metadata consists of tags and valid/invalid bits). 5. Starting from power on, the following byte-addressed cache references are recorded for the cache in the previous exercise: 0, 4, 16, 132, 232, 160, 1024, 30, 140, 3100, 180, 2180 a. How many blocks are replaced? b. What is the hit ratio? c. List the final state of the cache, with each valid entry represented as a record ofStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started