Answered step by step

Verified Expert Solution

Question

1 Approved Answer

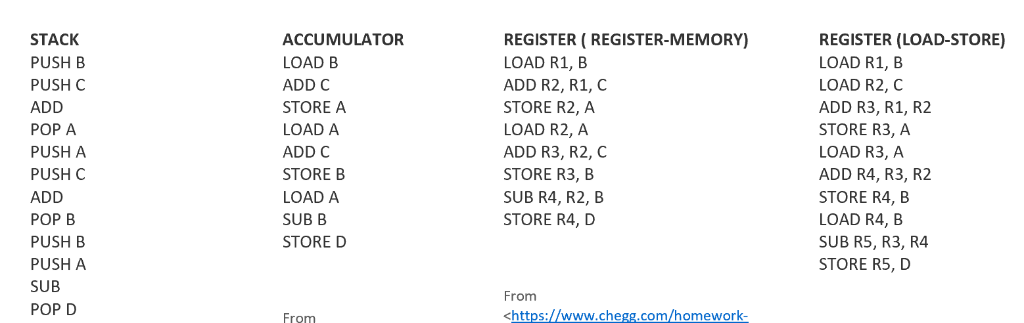

STACK PUSH B PUSH C ADD POP A PUSH A PUSH C ADD POP B PUSH B PUSH A SUB POP D ACCUMULATOR LOAD B

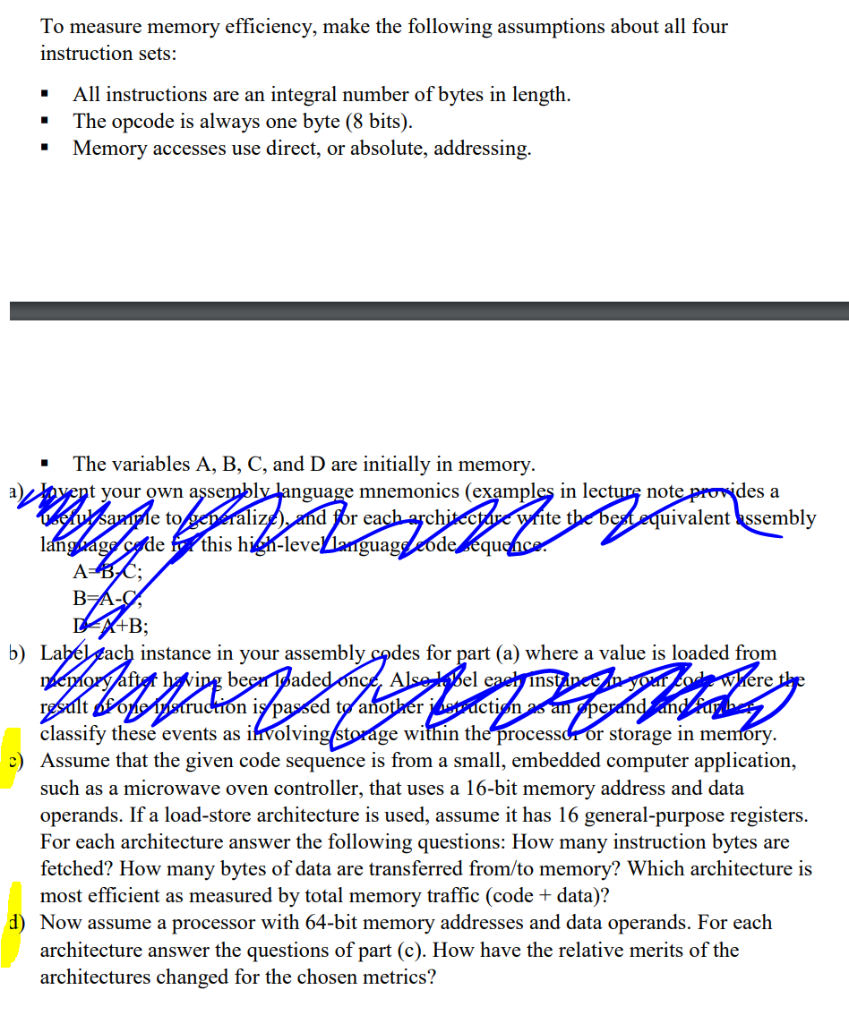

STACK PUSH B PUSH C ADD POP A PUSH A PUSH C ADD POP B PUSH B PUSH A SUB POP D ACCUMULATOR LOAD B ADD C STORE A LOAD A ADD C STORE B LOAD A SUB B STORE D REGISTER (REGISTER-MEMORY) LOAD R1, B ADD R2, R1, C STORE R2, A LOAD R2, A ADD R3, R2, C STORE R3, B SUB R4, R2, B STORE R4, D REGISTER (LOAD-STORE) LOAD R1, B LOAD R2, C ADD R3, R1, R2 STORE R3, A LOAD R3, A ADD R4, R3, R2 STORE R4, B LOAD R4, B SUB R5, R3, R4 STORE R5, D From rom To measure memory efficiency, make the following assumptions about all four nstruction sets: * " * All instructions are an integral number of bytes in length The opcode is always one byte (8 bits) Memory accesses use direct, or absolute, addressing The variables A, B, C, and D are initially in memory " t your own assembl nguage mnemonics (examples in lecture not des a d yor each arch Wiite t uivalent assembly b) Labeltach instance in your assembly codes for part (a) where a value is loaded from beer Iaded el e agt ins ere ct classify thes events as ihvolving storage within the processdr r storage in memory c) Assume that the given code sequence is from a small, embedded computer application, such as a microwave oven controller, that uses a 16-bit memory address and data operands. If a load-store architecture is used, assume it has 16 general-purpose registers For each architecture answer the following questions: How many instruction bytes are fetched? How many bytes of data are transferred from/to memory? Which architecture is most efficient as measured by total memory traffic (code + data)? d) Now assume a processor with 64-bit memory addresses and data operands. For each architecture answer the questions of part (c). How have the relative merits of the architectures changed for the chosen metrics? STACK PUSH B PUSH C ADD POP A PUSH A PUSH C ADD POP B PUSH B PUSH A SUB POP D ACCUMULATOR LOAD B ADD C STORE A LOAD A ADD C STORE B LOAD A SUB B STORE D REGISTER (REGISTER-MEMORY) LOAD R1, B ADD R2, R1, C STORE R2, A LOAD R2, A ADD R3, R2, C STORE R3, B SUB R4, R2, B STORE R4, D REGISTER (LOAD-STORE) LOAD R1, B LOAD R2, C ADD R3, R1, R2 STORE R3, A LOAD R3, A ADD R4, R3, R2 STORE R4, B LOAD R4, B SUB R5, R3, R4 STORE R5, D From rom To measure memory efficiency, make the following assumptions about all four nstruction sets: * " * All instructions are an integral number of bytes in length The opcode is always one byte (8 bits) Memory accesses use direct, or absolute, addressing The variables A, B, C, and D are initially in memory " t your own assembl nguage mnemonics (examples in lecture not des a d yor each arch Wiite t uivalent assembly b) Labeltach instance in your assembly codes for part (a) where a value is loaded from beer Iaded el e agt ins ere ct classify thes events as ihvolving storage within the processdr r storage in memory c) Assume that the given code sequence is from a small, embedded computer application, such as a microwave oven controller, that uses a 16-bit memory address and data operands. If a load-store architecture is used, assume it has 16 general-purpose registers For each architecture answer the following questions: How many instruction bytes are fetched? How many bytes of data are transferred from/to memory? Which architecture is most efficient as measured by total memory traffic (code + data)? d) Now assume a processor with 64-bit memory addresses and data operands. For each architecture answer the questions of part (c). How have the relative merits of the architectures changed for the chosen metrics

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started