Answered step by step

Verified Expert Solution

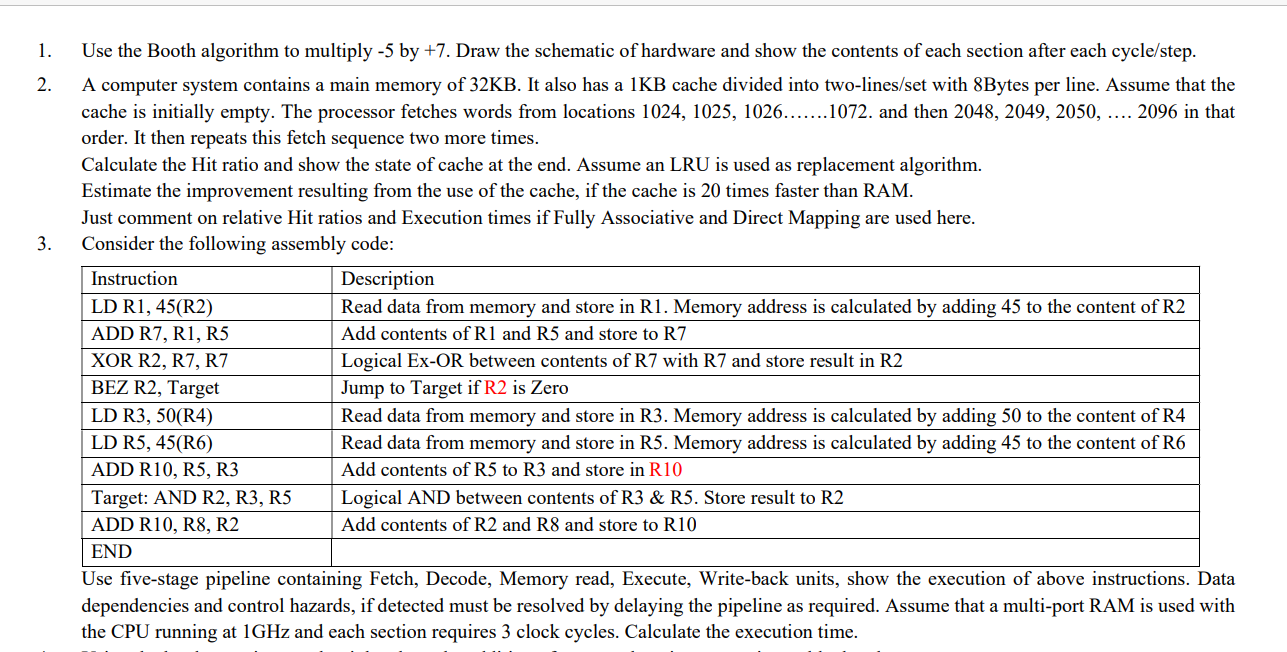

Question

1 Approved Answer

Subject - Computer Organization and Architecture [ Theory ] ///////// It's my 4th-time post for this questions answer. if you don't have enough knowledge for

Subject - Computer Organization and Architecture [ Theory ]

///////// It's my 4th-time post for this questions answer. if you don't have enough knowledge for solving this answer, please skip it.

Hi Experts! Would you please try to solve this as soon as possible with 100 % Accuracy? If possible, please do it.

You have to follow some instructions which I mentioned below. If you don't follow my instructions, please skip my questions.

You have to answer only #3 . I repeated, don't do other numbers.

Instructions are given,

- You need to show detailed calculations, as required.

- You need to provide clear diagrams, as required. All diagrams should be clearly drawn

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started