? Suppose that a computer has a processor with an L1 and an L2 cache. Let 7 be the access time for the L1 cache.

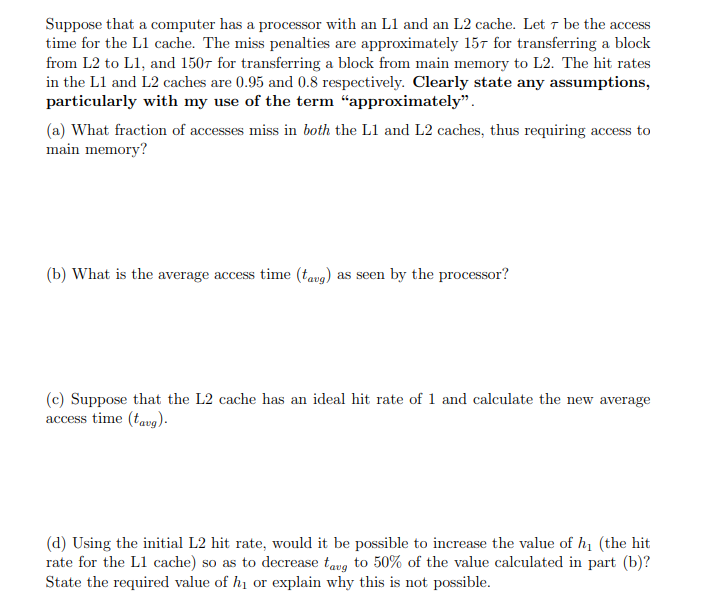

Suppose that a computer has a processor with an L1 and an L2 cache. Let 7 be the access time for the L1 cache. The miss penalties are approximately 157 for transferring a block from L2 to L1, and 1507 for transferring a block from main memory to L2. The hit rates in the L1 and L2 caches are 0.95 and 0.8 respectively. Clearly state any assumptions, particularly with my use of the term "approximately". (a) What fraction of accesses miss in both the L1 and L2 caches, thus requiring access to main memory? (b) What is the average access time (tag) as seen by the processor? (c) Suppose that the L2 cache has an ideal hit rate of 1 and calculate the new average access time (tavg). (d) Using the initial L2 hit rate, would it be possible to increase the value of h (the hit rate for the L1 cache) so as to decrease taug to 50% of the value calculated in part (b)? State the required value of h or explain why this is not possible.

Step by Step Solution

3.40 Rating (159 Votes )

There are 3 Steps involved in it

Step: 1

a when there will be is miss in both L1 and L2 then it will only ...

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started