Question: Test (Part B) Marks: 10 Answer ALL questions. Honesty Pledge: a) A hypothetical computer system has a hierarchical memory architecture consists of cache memory of

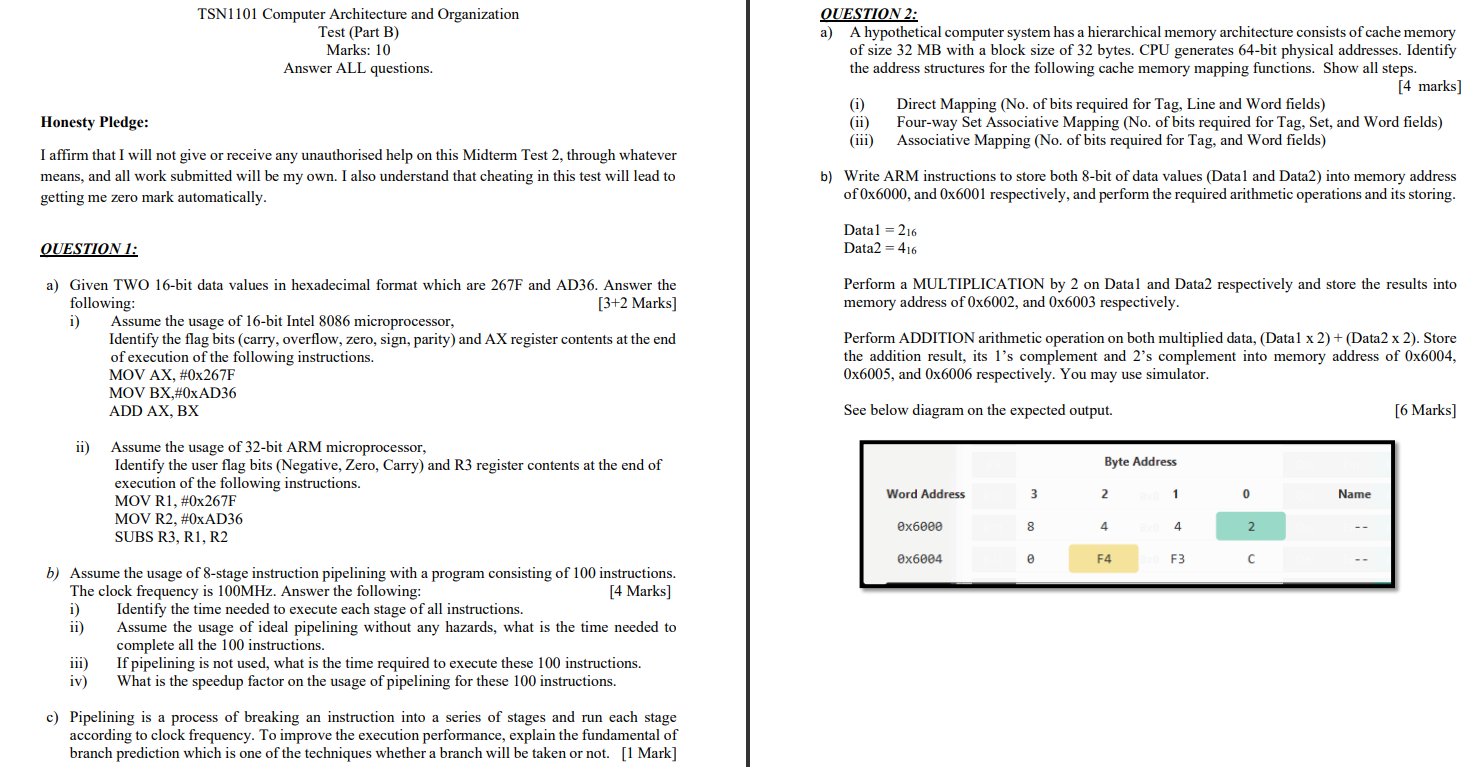

Test (Part B) Marks: 10 Answer ALL questions. Honesty Pledge: a) A hypothetical computer system has a hierarchical memory architecture consists of cache memory of size 32MB with a block size of 32 bytes. CPU generates 64-bit physical addresses. Identify the address structures for the following cache memory mapping functions. Show all steps. (i) Direct Mapping (No. of bits required for Tag, Line and Word fields) [4 marks] (ii) Four-way Set Associative Mapping (No. of bits required for Tag, Set, and Word fields) I affirm that I will not give or receive any unauthorised help on this Midterm Test 2, through whatever (iii) Associative Mapping (No. of bits required for Tag, and Word fields) means, and all work submitted will be my own. I also understand that cheating in this test will lead to b) Write ARM instructions to store both 8-bit of data values (Data1 and Data2) into memory address getting me zero mark automatically. of 06000, and 0x6001 respectively, and perform the required arithmetic operations and its storing. OUESTION 1: Data1=216Data2=416 a) Given TWO 16-bit data values in hexadecimal format which are 267F and AD36. Answer the Perform a MULTIPLICATION by 2 on Data1 and Data2 respectively and store the results into following: i) Assume the usage of 16-bit Intel 8086 microprocessor, memory address of 0x6002, and 0x6003 respectively. Identify the flag bits (carry, overflow, zero, sign, parity) and AX register contents at the end Perform ADDITION arithmetic operation on both multiplied data, (Data 12)+( Data2 2). Store of execution of the following instructions. the addition result, its 1's complement and 2's complement into memory address of 0x6004, MOV AX, \#0x267F 0x6005, and 0x6006 respectively. You may use simulator. MOV BX,\#0xAD36 ADD AX, BX See below diagram on the expected output. [6 Marks] ii) Assume the usage of 32-bit ARM microprocessor, Identify the user flag bits (Negative, Zero, Carry) and R3 register contents at the end of execution of the following instructions. MOV R1, \#0x267F MOV R2, \#0xAD36 SUBS R3, R1, R2 b) Assume the usage of 8-stage instruction pipelining with a program consisting of 100 instructions. The clock frequency is 100MHz. Answer the following: [4 Marks] i) Identify the time needed to execute each stage of all instructions. ii) Assume the usage of ideal pipelining without any hazards, what is the time needed to iii) If pipelining is not insed, what is iv) What is the is not used, what is the time required to execute these 100 instructions. c) Pipelining is a process of breaking an instruction into a series of stages and run each stage according to clock frequency. To improve the execution performance, explain the fundamental of branch prediction which is one of the techniques whether a branch will be taken or not. [1 Mark]

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts