Answered step by step

Verified Expert Solution

Question

1 Approved Answer

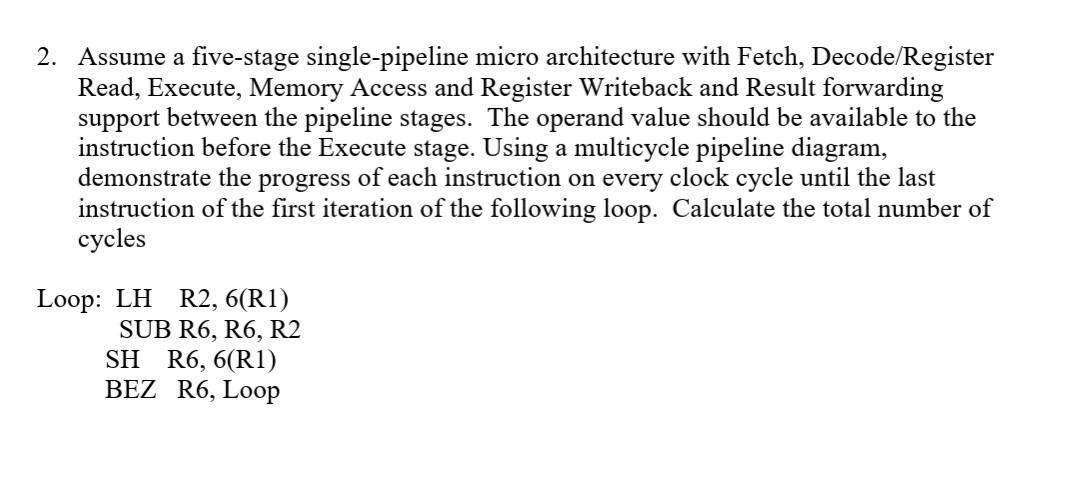

that is the whole question 2. Assume a five-stage single-pipeline micro architecture with Fetch, Decode/Register Read, Execute, Memory Access and Register Writeback and Result forwarding

that is the whole question

2. Assume a five-stage single-pipeline micro architecture with Fetch, Decode/Register Read, Execute, Memory Access and Register Writeback and Result forwarding support between the pipeline stages. The operand value should be available to the instruction before the Execute stage. Using a multicycle pipeline diagram, demonstrate the progress of each instruction on every clock cycle until the last instruction of the first iteration of the following loop. Calculate the total number of cycles Loop: LH R2, 6(R1) SUB R6, R6, R2 SH R6, 6(R1) BEZ R6, LoopStep by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started