Question: This exercise examines the effect of different cache designs, specifically comparing associative caches to the direct-mapped caches. For these exercises, refer to the sequence of

This exercise examines the effect of different cache designs, specifically comparing associative caches to the direct-mapped caches. For these exercises, refer to the sequence of word address shown below.

0x03, 0xb4, 0x2b, 0x02, 0xbe, 0x58, 0xbf, 0x0e, 0x1f, 0xb5, 0xbf, 0xba, 0x2e, 0xce

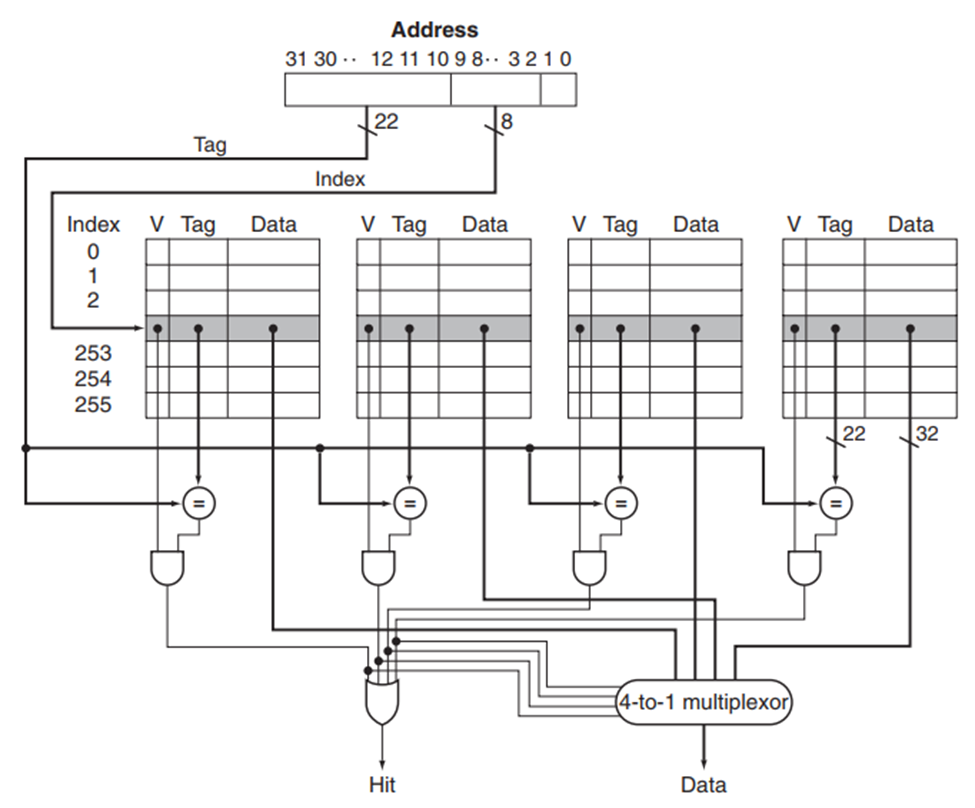

a) Sketch the organization of a three-way set associative cache with two-word blocks and a total size of 48 words. Your sketch should have a style similar to following Figure 5.18 below, but clearly show the width of the tag and data fields.

b) Trace the behavior of the cache from Exercise Q9.a. Assume a true LRU replacement policy. For each reference, identify

the binary word address,

the tag,

the index,

the offset

whether the reference is a hit or a miss, and

which tags are in each way of the cache after the reference has been handled.

c) Sketch the organization of a fully associative cache with oneword blocks and a total size of eight words. Your sketch should have a style similar to Figure 5.18, but clearly show the width of the tag and data fields.

Address

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts