Answered step by step

Verified Expert Solution

Question

1 Approved Answer

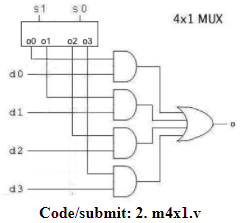

Using the verilog code and 2x1 decoder diagram shown below, write a program for the 4x1 decoder diagram. Use array syntax to declare a set

Using the verilog code and 2x1 decoder diagram shown below, write a program for the 4x1 decoder diagram. Use array syntax to declare a set of wires or registers.module DecoderMod(s, o); // module definition input s; output [0:1] o; not(o[0], s); assign o[1] = s; endmodule module MuxMod(s, d, o); input s; input [0:1] d; output o; wire [0:1] s_decoded, and_out; DecoderMod my_decoder(s, s_decoded); // create instance and(and_out[0], d[0], s_decoded[0]); and(and_out[1], d[1], s_decoded[1]); or(o, and_out[0], and_out[1]); endmodule module TestMod; reg s; reg [0:1] d; wire o; MuxMod my_mux(s, d, o); initial begin $display("Time s d o"); $display("--------------"); $monitor("%04d %b %b %b", $time, s, d, o); end initial begin s = 0; d = 2'b00; #1; s = 0; d = 2'b01; #1; s = 0; d = 2'b10; #1; s = 0; d = 2'b11; #1; s = 1; d = 2'b00; #1; s = 1; d = 2'b01; #1; s = 1; d = 2'b10; #1; s = 1; d = 2'b11; end endmodule

4x1 diagram:

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started