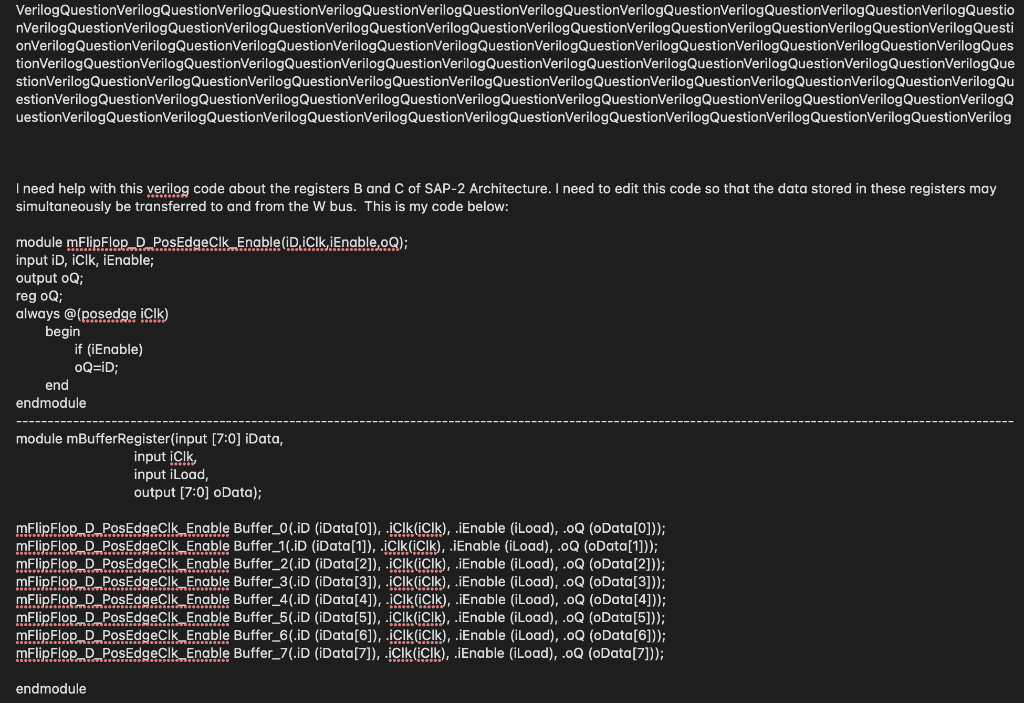

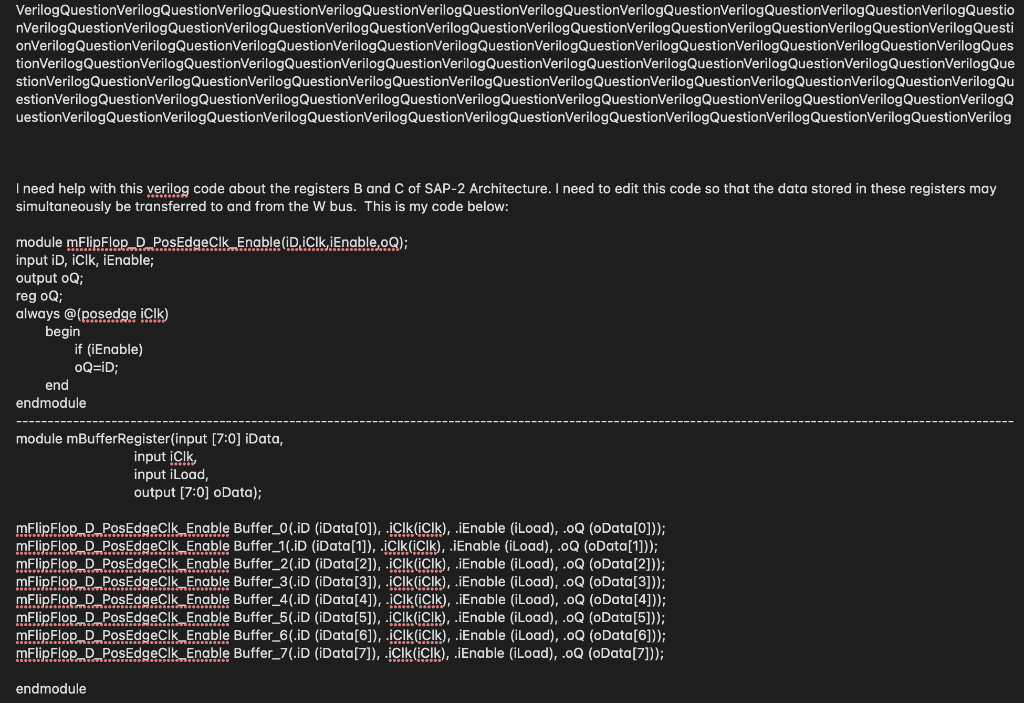

VerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestio nVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilogQuestionVerilog QuestionVerilogQuesti onVerilog QuestionVerilogQuestionVerilogQuestionVerilog QuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilog QuestionVerilogQues tionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilog QuestionVerilogQue stionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog Qu estionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilogQuestionVerilog QuestionVerilog QuestionVerilogQ uestionVerilogQuestionVerilogQuestionVerilog QuestionVerilog QuestionVerilogQuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog I need help with this verilog code about the registers B and C of SAP-2 Architecture. I need to edit this code so that the data stored in these registers may simultaneously be transferred to and from the W bus. This is my code below: module mFlipFlop D PosEdgeClk Enable(D.Clk, iEnable,oQ); input iD, iClk, iEnable; output oQ; reg oQ; always @(posedge iClk) begin if (iEnable) OQ=ID; end endmodule module mBuffer Register (input (7:0) iData, input iClk, input iLoad, output [7:0] oData); mFlipFlop D PosEdgeClk Enable Buffer_0(.iD (Data[0]), .iClk(iClk), .iEnable (iLoad), .oQ (oData[0])); mFlipFlop D PosEdgeClk Enable Buffer_1(.iD (iData[1]), .iClkiClk), .iEnable (iLoad),.oQ (oData[1])); mFlipFlop_D_PosEdgeClk_Enable Buffer_26.ID (iData[2]), iClk(iClk), .Enable (iLoad), .oQ (oData[2])); mFlipFlop D PosEdgeClk_Enable Buffer_3(.iD (iData[3]), .iClk(Clk), .iEnable (iLoad), .Q (oData[3])); mFlipFlop D PosEdgeClk_Enable Buffer_4.ID (iData[4]), .iClk(iClk), .Enable (iLoad), .oQ (oData[4])); mFlipFlop. D PosEdgeClk_Enable Buffer_5(.iD (iData[5]), .iClk(iClk), .iEnable (iLoad), .oQ (oData[5])); mFlipFlop D PosEdgeClk_Enable Buffer_6(.ID (iData[6]), .iClk(iClk), .iEnable (iLoad),.Q (oData[6])); mFlipFlop D PosEdgeClk Enable Buffer_7(.iD (iData[7]), .icik(iClk),.Enable (iLoad), .oQ (oData[7])); endmodule VerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestio nVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilogQuestionVerilog QuestionVerilogQuesti onVerilog QuestionVerilogQuestionVerilogQuestionVerilog QuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilog QuestionVerilogQues tionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilogQuestionVerilog QuestionVerilogQue stionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog Qu estionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilogQuestionVerilog QuestionVerilog QuestionVerilogQ uestionVerilogQuestionVerilogQuestionVerilog QuestionVerilog QuestionVerilogQuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog QuestionVerilog I need help with this verilog code about the registers B and C of SAP-2 Architecture. I need to edit this code so that the data stored in these registers may simultaneously be transferred to and from the W bus. This is my code below: module mFlipFlop D PosEdgeClk Enable(D.Clk, iEnable,oQ); input iD, iClk, iEnable; output oQ; reg oQ; always @(posedge iClk) begin if (iEnable) OQ=ID; end endmodule module mBuffer Register (input (7:0) iData, input iClk, input iLoad, output [7:0] oData); mFlipFlop D PosEdgeClk Enable Buffer_0(.iD (Data[0]), .iClk(iClk), .iEnable (iLoad), .oQ (oData[0])); mFlipFlop D PosEdgeClk Enable Buffer_1(.iD (iData[1]), .iClkiClk), .iEnable (iLoad),.oQ (oData[1])); mFlipFlop_D_PosEdgeClk_Enable Buffer_26.ID (iData[2]), iClk(iClk), .Enable (iLoad), .oQ (oData[2])); mFlipFlop D PosEdgeClk_Enable Buffer_3(.iD (iData[3]), .iClk(Clk), .iEnable (iLoad), .Q (oData[3])); mFlipFlop D PosEdgeClk_Enable Buffer_4.ID (iData[4]), .iClk(iClk), .Enable (iLoad), .oQ (oData[4])); mFlipFlop. D PosEdgeClk_Enable Buffer_5(.iD (iData[5]), .iClk(iClk), .iEnable (iLoad), .oQ (oData[5])); mFlipFlop D PosEdgeClk_Enable Buffer_6(.ID (iData[6]), .iClk(iClk), .iEnable (iLoad),.Q (oData[6])); mFlipFlop D PosEdgeClk Enable Buffer_7(.iD (iData[7]), .icik(iClk),.Enable (iLoad), .oQ (oData[7])); endmodule