Answered step by step

Verified Expert Solution

Question

1 Approved Answer

We will determine what the Accumulator (register R0) value will be after executing the machine language code using the template to the left to fill

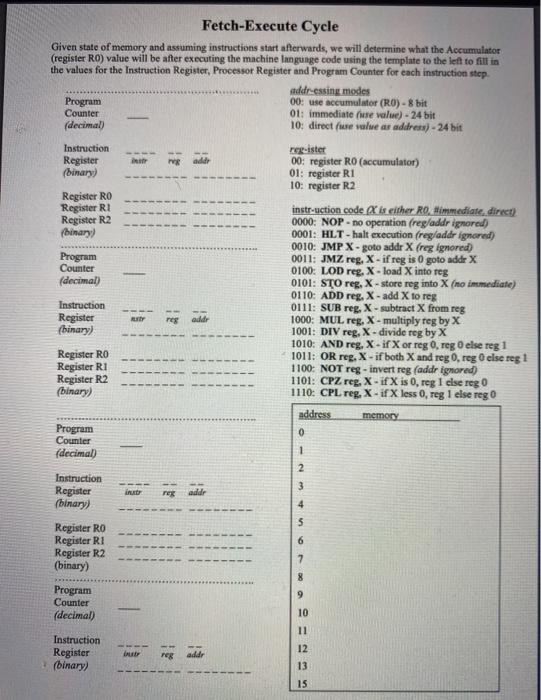

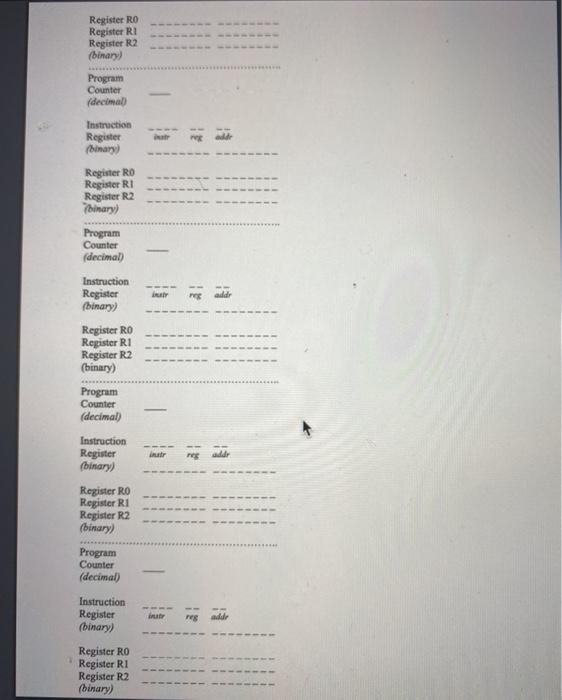

We will determine what the Accumulator (register R0) value will be after executing the machine language code using the template to the left to fill in the values for the instruction Register, Processor Register, and Program counter for each instruction step.

1 1 1 1 1 1 1 Fetch-Execute Cycle Given state of memory and assuming instructions start afterwards, we will determine what the Accumulator (register Ro) value will be after executing the machine langunge code using the template to the left to fill in the values for the Instruction Register, Processor Register and Program Counter for each instruction step addressing modes Program 00: use accumulator (RO) - 8 bit Counter 01: immediate evalue) - 24 bit (decimal 10: direct we value as address) - 24 bit Instruction rel-ister Register me addr 00: register RO (accumulator) (binar) 01: register R1 10: register R2 Register RO Register RI instruction code is either Rimmediate direct) Register R2 0000: NOP - no operation (regaddr ignored) (binary) 0001: HLT - halt execution (reg/addr ignored) 0010: JMP X - goto addr X freg ignored Program 0011: JMZ reg, X - if reg is 0 goto addr X Counter 0100: LOD reg. X - load X into reg (decimal) 0101: STO reg, X-store reg into X (no immediate) 0110: ADD reg, X-add X to reg Instruction 0111: SUB reg, X - subtract X from reg Register neg odds 1000: MUL reg. X-multiply reg by X (hinary) 1001: DIV reg, X. divide reg by X 1010: AND reg, X-if X or reg 0, reg else reg 1 Register RO 1011: OR reg. X - if both X and reg 0, reg else reg 1 Register RI 1100: NOT reg - invert reg (addr ignored) Register R2 1101: CPZ reg. X - if X is 0, reg 1 else reg 0 (binary) 1110: CPL reg. X-if X less 0, reg 1 else reg 0 address memory Program 0 Counter 1 (decimal 2 Instruction 3 Register PER addr (binary) 4 5 Register RO Register R1 6 Register R2 7 (binary) 8 Program 9 Counter 10 (decimal) 11 Instruction Register 12 negadir (binary) 13 15 Register RO Register RI Register R2 (binary) Program Counter (decimal Instruction Register finary) Register RO Register RI Register R2 Thinary) Program Counter (decimal) meg Instruction Register (binary) Register RO Register Ri Register R2 (binary) Program Counter (decimal) Instruction Register (binary) int Register RO Register Ri Register R2 (binary) Program Counter (decimal) Instruction Register (binary) reg Register RO Register R1 Register R2 (binary) 1 1 1 1 1 1 1 Fetch-Execute Cycle Given state of memory and assuming instructions start afterwards, we will determine what the Accumulator (register Ro) value will be after executing the machine langunge code using the template to the left to fill in the values for the Instruction Register, Processor Register and Program Counter for each instruction step addressing modes Program 00: use accumulator (RO) - 8 bit Counter 01: immediate evalue) - 24 bit (decimal 10: direct we value as address) - 24 bit Instruction rel-ister Register me addr 00: register RO (accumulator) (binar) 01: register R1 10: register R2 Register RO Register RI instruction code is either Rimmediate direct) Register R2 0000: NOP - no operation (regaddr ignored) (binary) 0001: HLT - halt execution (reg/addr ignored) 0010: JMP X - goto addr X freg ignored Program 0011: JMZ reg, X - if reg is 0 goto addr X Counter 0100: LOD reg. X - load X into reg (decimal) 0101: STO reg, X-store reg into X (no immediate) 0110: ADD reg, X-add X to reg Instruction 0111: SUB reg, X - subtract X from reg Register neg odds 1000: MUL reg. X-multiply reg by X (hinary) 1001: DIV reg, X. divide reg by X 1010: AND reg, X-if X or reg 0, reg else reg 1 Register RO 1011: OR reg. X - if both X and reg 0, reg else reg 1 Register RI 1100: NOT reg - invert reg (addr ignored) Register R2 1101: CPZ reg. X - if X is 0, reg 1 else reg 0 (binary) 1110: CPL reg. X-if X less 0, reg 1 else reg 0 address memory Program 0 Counter 1 (decimal 2 Instruction 3 Register PER addr (binary) 4 5 Register RO Register R1 6 Register R2 7 (binary) 8 Program 9 Counter 10 (decimal) 11 Instruction Register 12 negadir (binary) 13 15 Register RO Register RI Register R2 (binary) Program Counter (decimal Instruction Register finary) Register RO Register RI Register R2 Thinary) Program Counter (decimal) meg Instruction Register (binary) Register RO Register Ri Register R2 (binary) Program Counter (decimal) Instruction Register (binary) int Register RO Register Ri Register R2 (binary) Program Counter (decimal) Instruction Register (binary) reg Register RO Register R1 Register R2 (binary)

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started