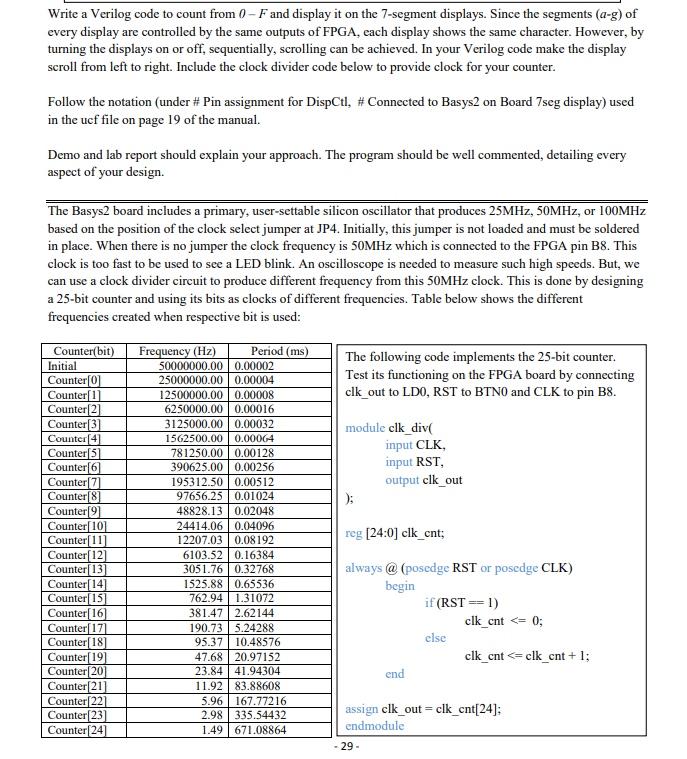

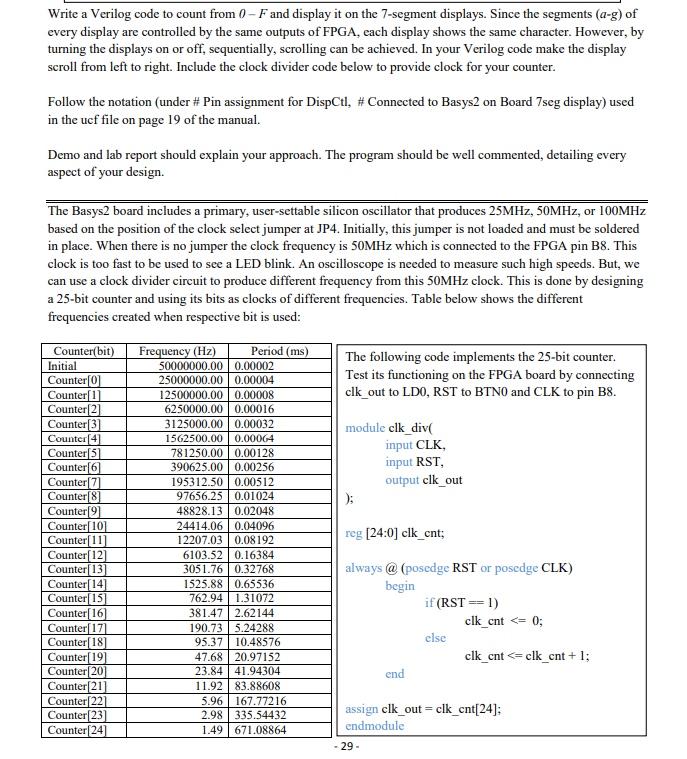

Write a Verilog code to count from 0- Fand display it on the 7-segment displays. Since the segments (a-g) of every display are controlled by the same outputs of FPGA, each display shows the same character. However, by turning the displays on or off, sequentially, scrolling can be achieved. In your Verilog code make the display scroll from left to right. Include the clock divider code below to provide clock for your counter. Follow the notation (under # Pn assignment for DispCtl, # Connected to Basys2 on Board 7seg display) used in the ucf file on page 19 of the manual. Demo and lab report should explain your approach. The program should be well commented, detailing every aspect of your design. The Basys2 board includes a primary, user-settable silicon oscillator that produces 25MHz, 50MHz, or 100MHz based on the position of the clock select jumper at JP4. Initially, this jumper is not loaded and must be soldered in place. When there is no jumper the clock frequency is 50MHz which is connected to the FPGA pin B8. This clock is too fast to be used to see a LED blink. An oscilloscope is needed to measure such high speeds. But, we can use a clock divider circuit to produce different frequency from this 50MHz clock. This is done by designing a 25-bit counter and using its bits as clocks of different frequencies. Table below shows the different frequencies created when respective bit is used: Counter(bit Frequency (Hz Period (ms 50000000.00 0.00002 25000000.00 0.00004 12500000.00 0,00008 6250000.00 0.00016 3125000.00 0.00032 The following code implements the 25-bit counter Test its functioning on the FPGA board by connecting clk out to LDO, RST to BTNO and CLK to pin B8. CounterO Counter1 Counter 2 Counter 3 Counterl4 Counter 5 Counter 6 Counter 7 Counter 8 Counter9 Counter 10 Counter 11 Counter 12 Counter 13 Counter 14 Counter 15 Counter 16 Counter17 Counter 18 Counter 19 Counter 20 Counter 21 Counter 22 Counter 23 Counter 24 module clk_div( 1562500.00 0.0000 input CLK, input RST output clk out 781250.00 0.00128 195312.50 0.00512 97656.25 0.01024 48828.13 0.02048 24414.06 0.04096 12207.03 0.08192 6103.52 0.16384 reg [24:0] clk_cnt; always @ (posedge RST or posedge CLK) 1525.88 0.65536 762.941.31072 381.472.62144 190.73 5.24288 in if (RST1) clk cnt