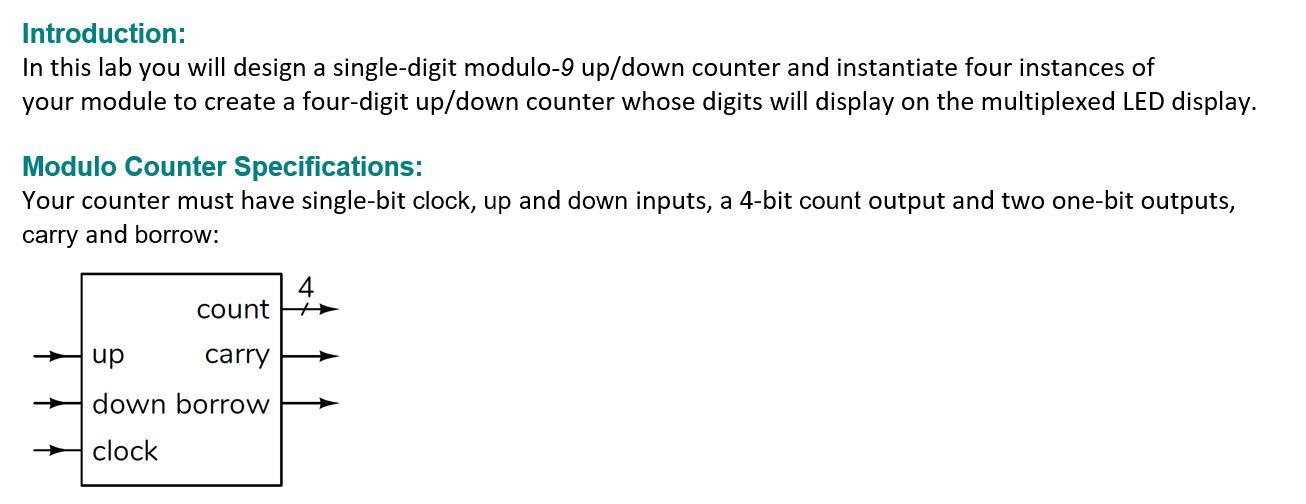

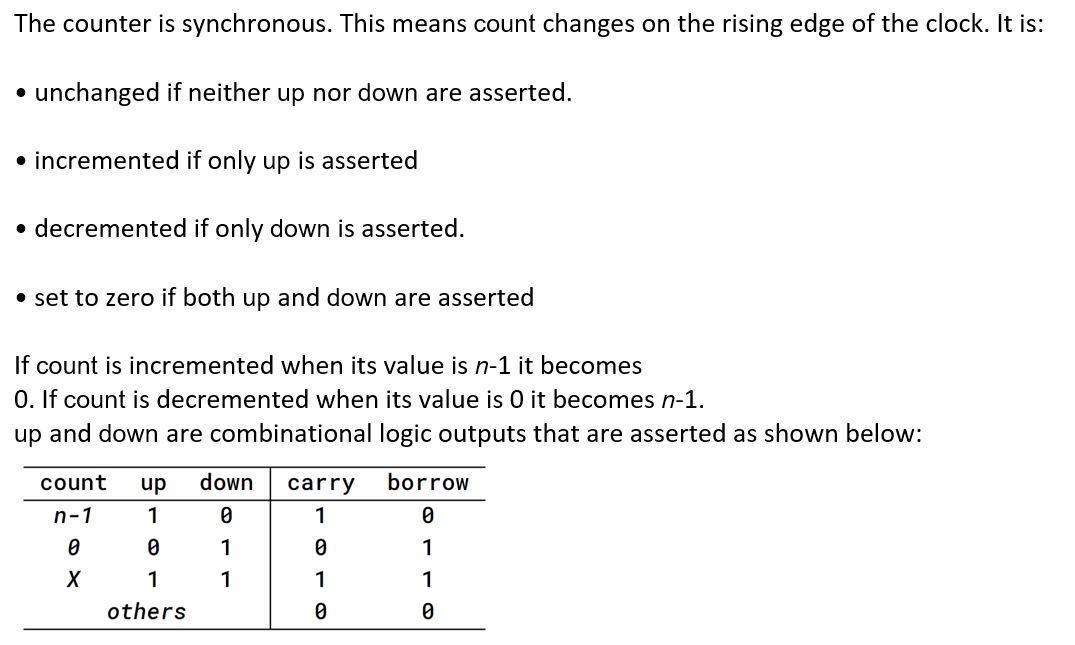

Question: Write a Verilog module for a 9-bit counter for two pushbuttons, 4-digit 7 segment display: / Use this file as your 'lab3' project top level

Write a Verilog module for a 9-bit counter for two pushbuttons, 4-digit 7 segment display:

![output logic [3:0] en, // digit enables output logic a, b, c,](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f0a22181481_17766f0a22125e8d.jpg)

![up/down pushbuttons ) ; logic [3:0] count[4] ; // counter values logic](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f0a222d50e2_17866f0a2224ffa6.jpg)

![up[4], down[4] ; // up/down inputs logic reset, reset_next ; // "sticky"](https://dsd5zvtm8ll6.cloudfront.net/si.experts.images/questions/2024/09/66f0a2236f84b_17966f0a22312786.jpg)

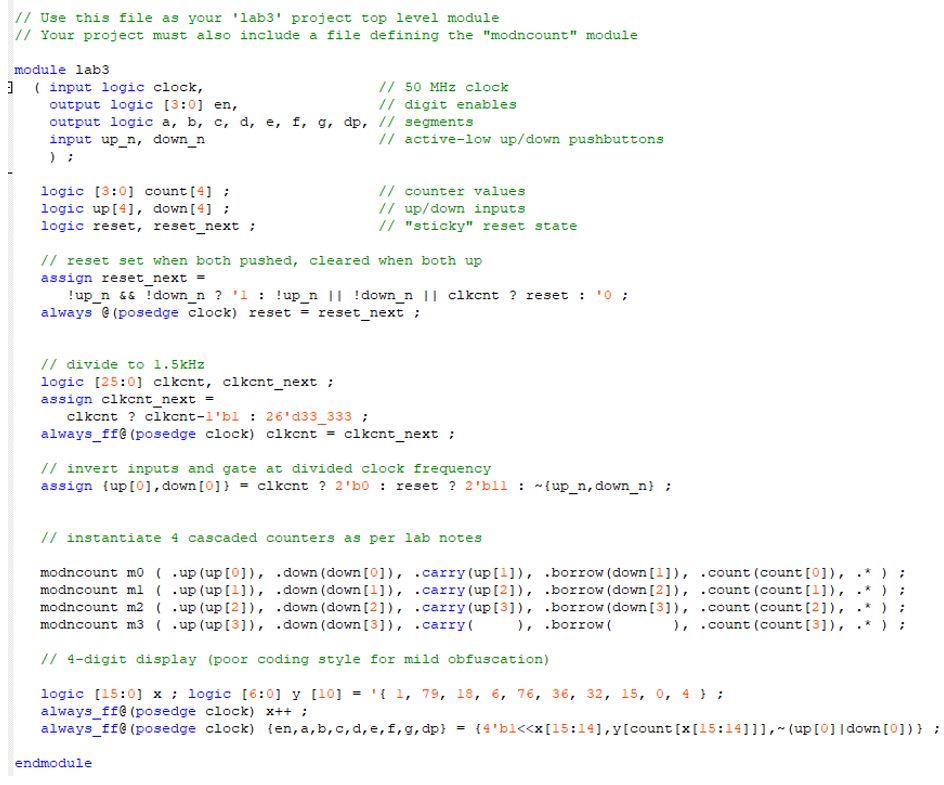

/ Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modncount" module

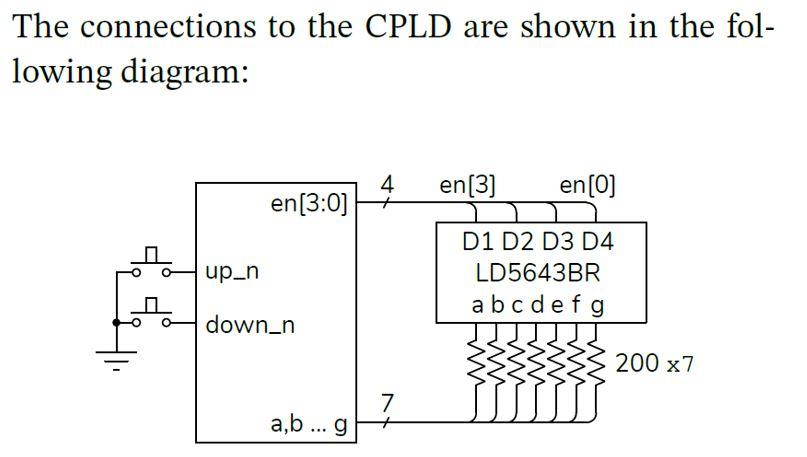

module lab3 ( input logic clock, // 50 MHz clock output logic [3:0] en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons ) ; logic [3:0] count[4] ; // counter values logic up[4], down[4] ; // up/down inputs logic reset, reset_next ; // "sticky" reset state

// reset set when both pushed, cleared when both up assign reset_next = !up_n && !down_n ? '1 : !up_n || !down_n || clkcnt ? reset : '0 ; always @(posedge clock) reset = reset_next ; // divide to 1.5kHz logic [25:0] clkcnt, clkcnt_next ; assign clkcnt_next = clkcnt ? clkcnt-1'b1 : 26'd33_333 ; always_ff@(posedge clock) clkcnt = clkcnt_next ; // invert inputs and gate at divided clock frequency assign {up[0],down[0]} = clkcnt ? 2'b0 : reset ? 2'b11 : ~{up_n,down_n} ;

// instantiate 4 cascaded counters as per lab notes

modncount m0 ( .up(up[0]), .down(down[0]), .carry(up[1]), .borrow(down[1]), .count(count[0]), .* ) ; modncount m1 ( .up(up[1]), .down(down[1]), .carry(up[2]), .borrow(down[2]), .count(count[1]), .* ) ; modncount m2 ( .up(up[2]), .down(down[2]), .carry(up[3]), .borrow(down[3]), .count(count[2]), .* ) ; modncount m3 ( .up(up[3]), .down(down[3]), .carry( ), .borrow( ), .count(count[3]), .* ) ; // 4-digit display (poor coding style for mild obfuscation) logic [15:0] x ; logic [6:0] y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4 } ; always_ff@(posedge clock) x++ ; always_ff@(posedge clock) {en,a,b,c,d,e,f,g,dp} = {4'b1

endmodule

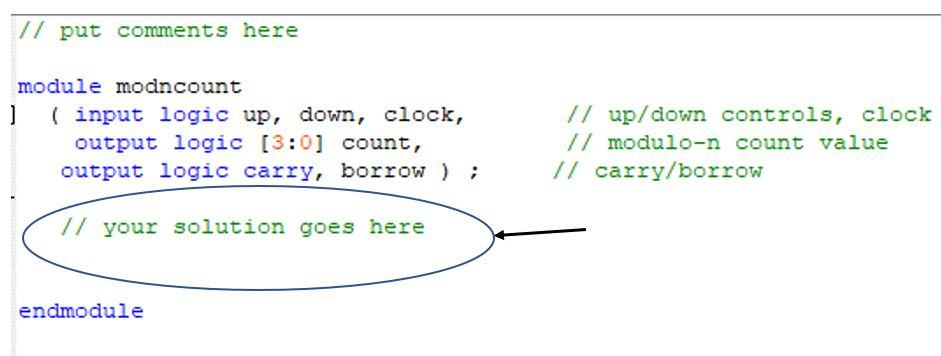

// put comments here

module modncount ( input logic up, down, clock, // up/down controls, clock output logic [3:0] count, // modulo-9 count value output logic carry, borrow ) ; // carry/borrow

// your solution goes here

endmodule

// Use this file as your 'lab3' project top level module // Your project must also include a file defining the "modncount" module module lab3 : ( input logic clock, 7/ 50 MHz clock output logic (3:0) en, // digit enables output logic a, b, c, d, e, f, g, dp, // segments input up_n, down_n // active-low up/down pushbuttons logic (3:0) count(4) ; logic up[4], down[4]; logic reset, reset_next; // counter values // up/down inputs // "sticky" reset state // reset set when both pushed, cleared when both up assign reset_next = ! up_n && !down_n ? '1 : !up_n || ! down_n 11 clkent ? reset : ' ; always @ (posedge clock) reset = reset_next; // divide to 1.5kHz logic (25:0) clkent, clkcnt_next ; assign clkcnt_next = clkcnt ? clkcnt-l'bi : 26'd33_333; always_ff@ (posedge clock) clkent = clkcnt_next; // invert inputs and gate at divided clock frequency assign {up [0], down[0]) = clkent ? 2'bo : reset ? 2'bll : ~{up_n, down_n) ; // instantiate 4 cascaded counters as per lab notes : modncount mo ( .up (up[0]), .down (down[0]), .carry(up[1]), .borrow (down[1]), .count (count[0), .*) modncount ml ( .up (up[-]), down (down[1]), .carry (up [2]), borrow (down[2]), .count (count [1]), .*); modncount m2 ( .up (up [2]), .down (down (21), .carry(up [3]), .borrow (down (31), .count (count [2]), > ; modncount m3 ( .up (up [3]), .down (down[3]), .carry ), borrow ), .count (count [3]), 1/4-digit display (poor coding style for mild obfuscation) logic (15:0] x ; logic [6:0] Y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4); always_ff@ (posedge clock) x++; always_ff@ (posedge clock) (en, a, b, c, d, e, f, g, dp) = {4'bi ; modncount m3 ( .up (up [3]), .down (down[3]), .carry ), borrow ), .count (count [3]), 1/4-digit display (poor coding style for mild obfuscation) logic (15:0] x ; logic [6:0] Y [10] = '{ 1, 79, 18, 6, 76, 36, 32, 15, 0, 4); always_ff@ (posedge clock) x++; always_ff@ (posedge clock) (en, a, b, c, d, e, f, g, dp) = {4'bi

Step by Step Solution

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts