Question

Write a VHDL entity for the full adder sub-circuit and write a top-level VHDL entity that instantiates four instances of this full adder. 2. Compile

Write a VHDL entity for the full adder sub-circuit and write a top-level VHDL entity that instantiates four instances of this full adder. 2. Compile your code and use timing simulation to verify the correct operation of the circuit by using different values for A, B and the carry-in cin of the adder. Write a VHDL entity for the full adder sub-circuit and write a top-level VHDL entity that instantiates four instances of this full adder. 2. Compile your code and use timing simulation to verify the correct operation of the circuit by using different values for A, B and the carry-in cin of the adder.

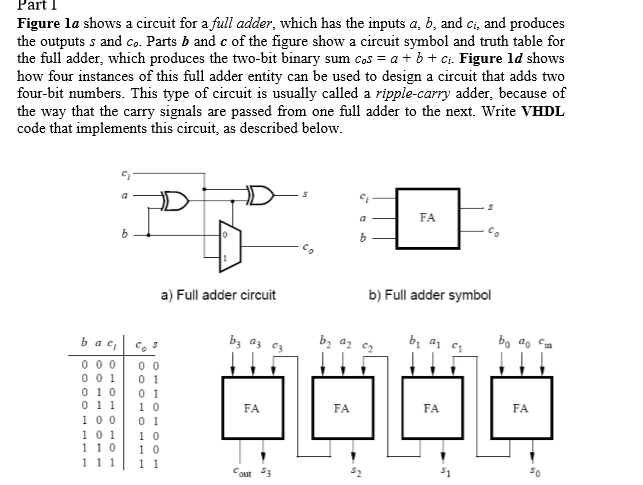

Part Figure la shows a circuit for a full adder, which has the inputs a, b, and ci, and produces the outputs s and co. Parts b and c of the figure show a circuit symbol and truth table for the full adder, which produces the two-bit binary sum Cos = a + b + c. Figure 1d shows how four instances of this full adder entity can be used to design a circuit that adds two four-bit numbers. This type of circuit is usually called a ripple-carry adder, because of the way that the carry signals are passed from one full adder to the next. Write VHDL code that implements this circuit, as described below l FA a) Full adder circuit b) Full adder symbol b acco b, a eebo a i 0 0 0 o 0 00 01 010 0 1 01 10 1 0001 1010 11010 FA FA FA FA Cout 3

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started