Answered step by step

Verified Expert Solution

Question

1 Approved Answer

.Write VHDL code to generate Clock signal with the specified period using 50 MHz clock signal available on your development board. Use the SWO

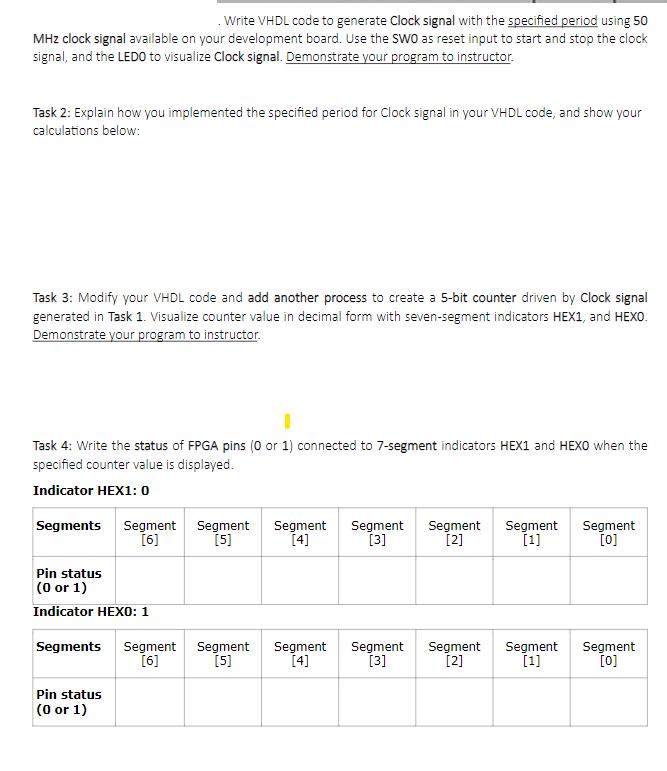

.Write VHDL code to generate Clock signal with the specified period using 50 MHz clock signal available on your development board. Use the SWO as reset input to start and stop the clock signal, and the LEDO to visualize Clock signal. Demonstrate your program to instructor. Task 2: Explain how you implemented the specified period for Clock signal in your VHDL code, and show your calculations below: Task 3: Modify your VHDL code and add another process to create a 5-bit counter driven by Clock signal generated in Task 1. Visualize counter value in decimal form with seven-segment indicators HEX1, and HEXO. Demonstrate your program to instructor. Task 4: Write the status of FPGA pins (0 or 1) connected to 7-segment indicators HEX1 and HEXO when the specified counter value is displayed. Indicator HEX1: 0 [1] Segments Segment Segment Segment Segment Segment Segment [6] [5] [4] [3] [2] Pin status (0 or 1) Indicator HEXO: 1 Segments Segment [6] Pin status (0 or 1) Segment [5] Segment [4] Segment Segment Segment [3] [2] [1] Segment [0] Segment [0]

Step by Step Solution

★★★★★

3.39 Rating (158 Votes )

There are 3 Steps involved in it

Step: 1

Below is a VHDL code snippet for the specified tasks Please note that you mi...

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started