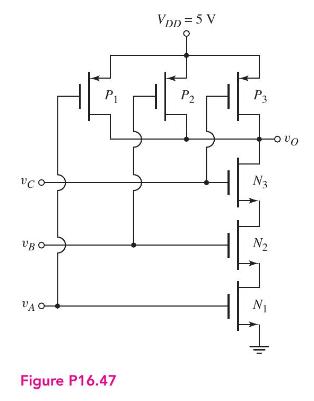

Consider the three-input CMOS NAND circuit in Figure P16.47. Assume (k_{n}^{prime}=2 k_{p}^{prime}) and (V_{T N}=left|V_{T P} ight|=0.8

Question:

Consider the three-input CMOS NAND circuit in Figure P16.47. Assume \(k_{n}^{\prime}=2 k_{p}^{\prime}\) and \(V_{T N}=\left|V_{T P}\right|=0.8 \mathrm{~V}\).

(a) If \(v_{A}=v_{B}=5 \mathrm{~V}\), determine \(v_{C}\) such that both \(N_{3}\) and \(P_{3}\) are biased in the saturation region when \((W / L)_{p}=\) \(2(W / L)_{n}\). (State any assumptions you make.)

(b) If \(v_{A}=v_{B}=v_{C}=v_{I}\), determine the relationship between \((W / L)_{p}\) and \((W / L)_{n}\) such that \(v_{I}=2.5 \mathrm{~V}\) when all transistors are biased in the saturation region.

(c) Using the results of part (b) and assuming \(v_{A}=v_{B}=5 \mathrm{~V}\), determine \(v_{C}\) such that both \(N_{3}\) and \(P_{3}\) are biased in the saturation region. (State any assumptions you make.)

Step by Step Answer:

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen