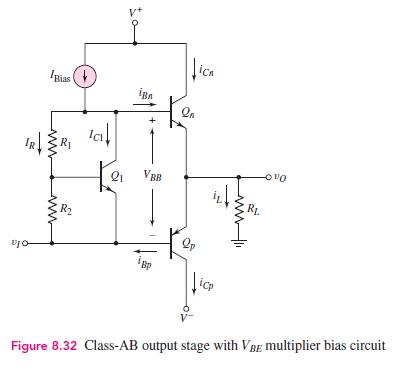

Question: Design the class-AB output stage with the (V_{B E}) multiplier in Figure 8.32 to deliver an average of (1 mathrm{~W}) to an (8 Omega) load.

Design the class-AB output stage with the \(V_{B E}\) multiplier in Figure 8.32 to deliver an average of \(1 \mathrm{~W}\) to an \(8 \Omega\) load. The peak output voltage must be no more than 80 percent of \(V^{+}\). Let \(V^{-}=-V^{+}\). Specify the circuit and transistor parameters.

V+ Bias iBn Jica IRRI www R VBB jo Bp icp R Figure 8.32 Class-AB output stage with VBE multiplier bias circuit

Step by Step Solution

3.32 Rating (155 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts