On-line testing 0/ a half-adder Consider a half-adder wh ich provides the sum and carry functions: s

Question:

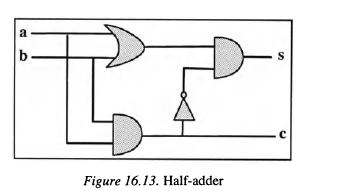

On-line testing 0/ a half-adder Consider a half-adder wh ich provides the sum and carry functions: s = a Ei' b and c = a.b. This circuit was realized by logic gates according to the schema in Figure 16.13. We consider the 'stuck-at 0 and 1 of inputs and outputs of gates' fault model.

1. Analyze the existing functional redundancies of this circuit. Deduce the on-line detection capability of this circuit. Discuss the limits of this property.

2. Modify this circuit by adding an output noted p, to create a parity code. In this way, does it detect every single or multiple eITors of the complete circuit? Discuss the checker characteristics.

3. Modify the previous circuit by using distinct (independent) logic circuits for each output. What improvements does this therefore bring? What faults remain undetected on-line?

4. Study the same thing with a duplex structure. Analyze every detected single or multiple faults and those that are not detected. Discuss the checker that is necessary for this structure.

Step by Step Answer:

Design Of Dependable Computing Systems

ISBN: 978-9048159413

1st Edition

Authors: J C Geffroy ,G Motet