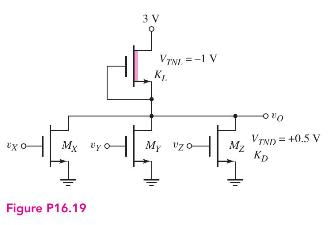

Consider the three-input NOR logic gate in Figure P16.19. The transistor parameters are (V_{T N L}=-1 mathrm{~V})

Question:

Consider the three-input NOR logic gate in Figure P16.19. The transistor parameters are \(V_{T N L}=-1 \mathrm{~V}\) and \(V_{T N D}=0.5 \mathrm{~V}\). The maximum value of \(v_{O}\) in its low state is to be \(0.1 \mathrm{~V}\).

(a) Determine \(K_{D} / K_{L}\).

(b) The maximum power dissipation in the NOR logic gate is to be \(0.1 \mathrm{~mW}\). Determine the width-to-length ratios of the transistors.

(c) Determine \(v_{O}\) when \(v_{X}=v_{Y}=\) \(v_{Z}=3 \mathrm{~V}\).

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Microelectronics Circuit Analysis And Design

ISBN: 9780071289474

4th Edition

Authors: Donald A. Neamen

Question Posted: