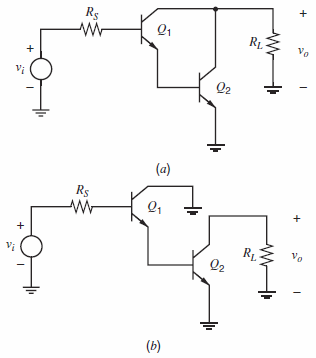

A Darlington stage and a common-collectorcommon-emitter cascade are shown schematically in Fig. 7.40, where R S =

Question:

(a) Calculate the low-frequency small-signal voltage gain Ï…o/Ï…i for each circuit.

(b) Use the zero-value time-constant method to calculate the ˆ’3-dB frequency of the gain of each circuit. Data: β = 100, fT = 500 MHz at IC = 1 mA, Cμ = 0.4 pF,Cje = 2 pF, Ccs = 1 pF, rb = 0, ro = ˆž, IC1 = 10 µA, and IC2 = 1mA. (Values of Cμ, Ccs, and Cje are at the bias point.)

Fig. 7.40:

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Analysis and Design of Analog Integrated Circuits

ISBN: 978-0470245996

5th edition

Authors: Paul R. Gray, Paul J. Hurst Stephen H. Lewis, Robert G. Meyer

Question Posted: