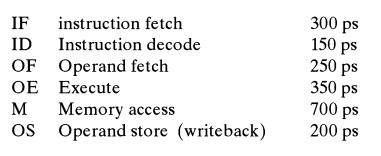

Question: A processor executes an instruction in the following six stages. The time required by each stage in picoseconds (1,000 ps = 1 ns) is given

A processor executes an instruction in the following six stages. The time required by each stage in picoseconds (1,000 ps = 1 ns) is given for each stage.

a. What is the time to execute an instruction if the processor is not pipelined?

b. What is the time taken to fully execute an instruction assuming that this structure is pipelined in six stages and that there is an additional 20 ps per stage due to the pipeline latches?

c. Once the pipeline is full, what is the average instruction rate?

d. Suppose that 25% of instructions are branch instructions that are taken and cause a 3-cycle penalty, what is the effective instruction execute time?

IF instruction fetch ID Instruction decode OF Operand fetch OE Execute M Memory access OS Operand store (writeback) 300 ps 150 ps 250 ps 350 ps 700 ps 200 ps

Step by Step Solution

3.50 Rating (160 Votes )

There are 3 Steps involved in it

a Add up the individual times 300 150 250 350 700 2001950ps 1950ns b The longest stage ... View full answer

Get step-by-step solutions from verified subject matter experts