Question: One proposed solution for the problem of false sharing is to add a valid bit per word. This would allow the protocol to invalidate a

One proposed solution for the problem of false sharing is to add a valid bit per word. This would allow the protocol to invalidate a word without removing the entire block, letting a processor keep a portion of a block in its cache while another processor writes a different portion of the block. What extra complications are introduced into the basic snooping cache coherence protocol (Figure 5.7) if this capability is included? Remember to consider all possible protocol actions.

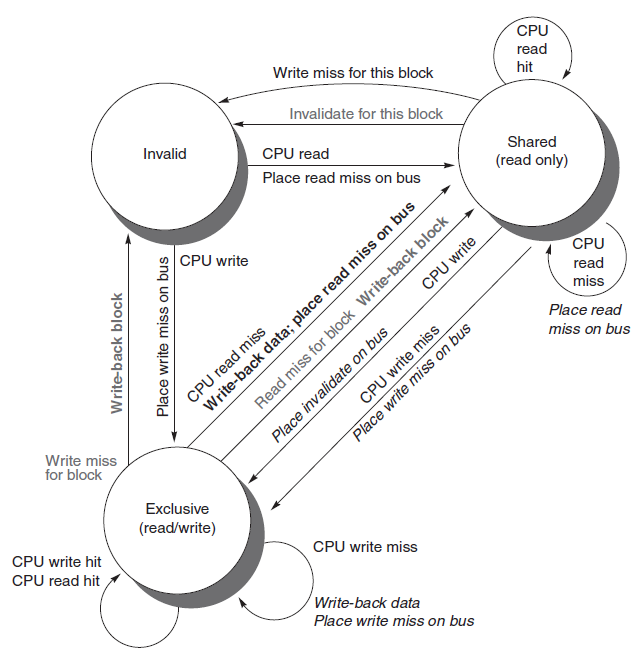

Figure 5.7

CPU Write miss for this block read hit Invalidate for this block Invalid CPU read Shared (read only) Place read miss on bus CPU read miss Write-back data; place read miss on bus CPU write CPU read CPU write miss Place read miss on bus CPU write miss Write miss for block Place invalidate on bus Place write miss on bus Exclusive (read/write) CPU write hit CPU read hit CPU write miss Write-back data Place write miss on bus Write-back block Place write miss on bus Read miss for block Write-back block

Step by Step Solution

3.35 Rating (161 Votes )

There are 3 Steps involved in it

An obvious complication introduced by providing a valid bit per word is the need to match not on... View full answer

Get step-by-step solutions from verified subject matter experts