Question: For a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache. 1. What is the

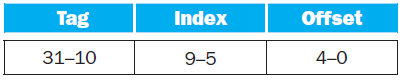

For a direct-mapped cache design with a 32-bit address, the following bits of the address are used to access the cache.

1. What is the cache block size (in words)?

2. How many entries does the cache have?

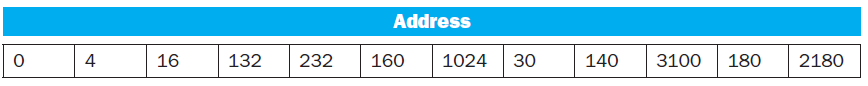

3. What is the ratio between total bits required for such a cache implementation over the data storage bits? Starting from power on, the following byte-addressed cache references are recorded.

4. How many blocks are replaced?

5. What is the hit ratio?

6. List the final state of the cache, with each valid entry represented as a record of .

Tag Index Offset 31-10 9-5 4-0 Address 140 4 16 132 232 160 1024 30 3100 180 2180

Step by Step Solution

3.27 Rating (176 Votes )

There are 3 Steps involved in it

1 8 2 32 3 1 22832 1086 4 3 5 0... View full answer

Get step-by-step solutions from verified subject matter experts