Question: Repeat 4.33.2, but this time every executed instruction has a RAW data dependence to the instruction that executes right after it. You can assume that

Repeat 4.33.2, but this time every executed instruction has a RAW data dependence to the instruction that executes right after it. You can assume that no stall cycles are needed, i.e., forwarding allows consecutive instructions to execute in back-to-back cycles.

Exercise 4.33.2

If there are no branch mispredictions and no data dependences, what is the expected performance improvement over a 1-issue processor with the classical 5-stage pipeline? Assume that the clock cycle time decreases in proportion to the number of pipeline stages.

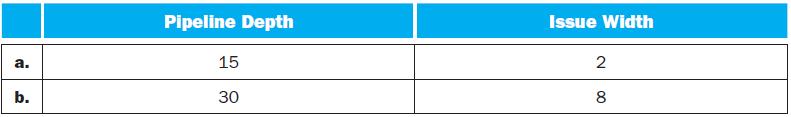

This exercise explores how branch prediction affects performance of a deeply pipelined multiple-issue processor. Problems in this exercise refer to a processor with the following number of pipeline stages and instructions issued per cycle:

a. b. Pipeline Depth 15 30 Issue Width 2 8

Step by Step Solution

3.47 Rating (147 Votes )

There are 3 Steps involved in it

In Exercise 4332 youre asked to consider a processor with a 5stage pipeline and a 2issue capability ... View full answer

Get step-by-step solutions from verified subject matter experts