Question: To support multiple virtual machines, two levels of memory virtualization are needed. Each virtual machine still controls the mapping of virtual address (VA) to physical

Consider the following sequence of operations: (1) Create process; (2) TLB miss; (3) page fault; (4) context switch;

1. What would happen for the given operation sequence for shadow page table and nested page table, respectively?

2. Assuming an x86-based 4-level page table in both guest and nested page table, how many memory references are needed to service a TLB miss for native vs. nested page table?

3. Among TLB miss rate, TLB miss latency, page fault rate, and page fault handler latency, which metrics are more important for shadow page table? Which are important for nested page table?

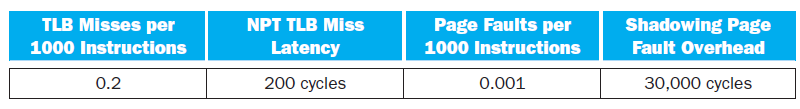

Assume the following parameters for a shadow paging system.

4. For a benchmark with native execution CPI of 1, what are the CPI numbers if using shadow page tables vs. NPT (assuming only page table virtualization overhead)?

5. What techniques can be used to reduce page table shadowing induced overhead?

6. What techniques can be used to reduce NPT induced overhead?

Page Faults per TLB Misses per 1000 Instructions NPT TLB Miss Shadowing Page 1000 Instructions Latency Fault Overhead 200 cycles 0.001 30,000 cycles 0.2

Step by Step Solution

3.55 Rating (173 Votes )

There are 3 Steps involved in it

1 Shadow page table 1 VM creates page table hypervisor updates shadow table ... View full answer

Get step-by-step solutions from verified subject matter experts