Question: What is the speedup that would be achieved by using four branch delay slots to reduce control hazards in this processor? Assume that there are

What is the speedup that would be achieved by using four branch delay slots to reduce control hazards in this processor? Assume that there are no data dependences between instructions and that all four delay slots can be illed with useful instructions without increasing the number of executed instructions. To make your computations easier, you can also assume that the mispredicted branch instruction is always the last instruction to be fetched in a cycle, i.e., no instructions that are in the same pipeline stage as the branch are fetched from the wrong path.

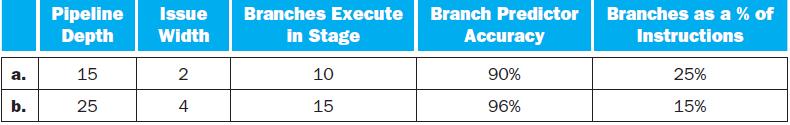

This exercise is intended to help you better understand the relationship between ISA design and pipelining. Problems in this exercise assume that we have a multiple issue pipelined processor with the following number of pipeline stages, instructions issued per cycle, stage in which branch outcomes are resolved, and branch predictor accuracy:

a. b. Pipeline Issue Width Depth 15 25 2 4 Branches Execute in Stage 10 15 Branch Predictor Accuracy 90% 96% Branches as a % of Instructions 25% 15%

Step by Step Solution

3.47 Rating (144 Votes )

There are 3 Steps involved in it

To calculate the speedup achieved by using four branch delay slots to reduce control hazards we need ... View full answer

Get step-by-step solutions from verified subject matter experts