What should happen if the processor issues a request that misses in the cache while a block

Question:

What should happen if the processor issues a request that misses in the cache while a block is being written back to main memory from the write buffer?

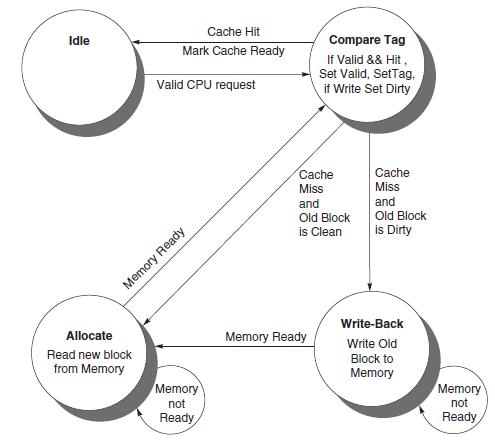

In this exercise, we will explore the control unit for a cache controller for a processor with a write buffer. Use the inite state machine found in Figure 5.34 as a starting point for designing your own inite state machines. Assume that the cache controller is for the simple direct-mapped cache described on page 529, but you will add a write buffer with a capacity of one block. Recall that the purpose of a write buffer is to serve as temporary storage so that the processor doesn't have to wait for two memory accesses on a dirty miss. Rather than writing back the dirty block before reading the new block, it buffers the dirty block and immediately begins reading the new block. The dirty block can then be written to main memory while the processor is working.

Step by Step Answer:

Computer Organization And Design The Hardware Software Interface

ISBN: 9780123747501

4th Revised Edition

Authors: David A. Patterson, John L. Hennessy