An article in the AT&T Technical Journal (March/April 1986, Vol. 65, pp. 39-50) describes the application of

Question:

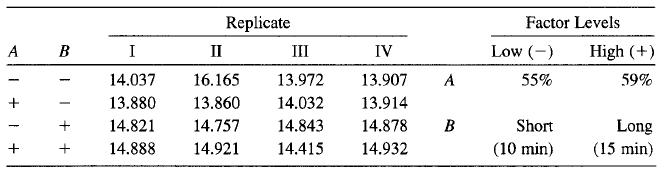

An article in the AT&T Technical Journal (March/April 1986, Vol. 65, pp. 39-50) describes the application of two-level factorial designs to integrated circuit manufacturing. A basic processing step is to grow an epitaxial layer on polished silicon wafers. The wafers mounted on a susceptor are positioned inside a bell jar, and chemical vapors are introduced. The susceptor is rotated and heat is applied until the epitaxial layer is thick enough. An experiment was run using two factors: arsenic flow rate (A) and deposition time (B). Four replicates were run, and the epitaxial layer thickness was measured (in tun). The data are shown below:

(a) Estimate the factor effects.

(b) Conduct an analysis of variance. Which factors are important?

(c) Write down a regression equation that could be used to predict epitaxial layer thickness over the region of arsenic flow rate and deposition time used in this experiment.

(d) Analyze the residuals. Are there any residuals that should cause concern?

(e) Discuss how you might deal with the potential outlier found in part (d).

Step by Step Answer: