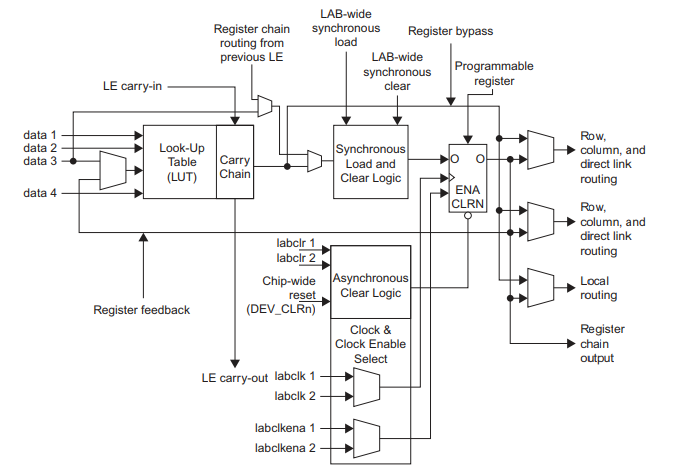

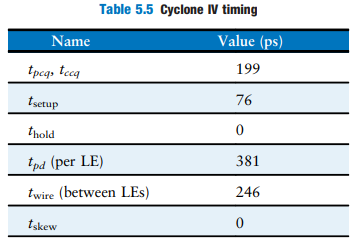

Question: Consider the Cyclone IV LE shown in Figure 5.58. According to the datasheet, it has the timing specifications given in Table 5.5.(a) What is the

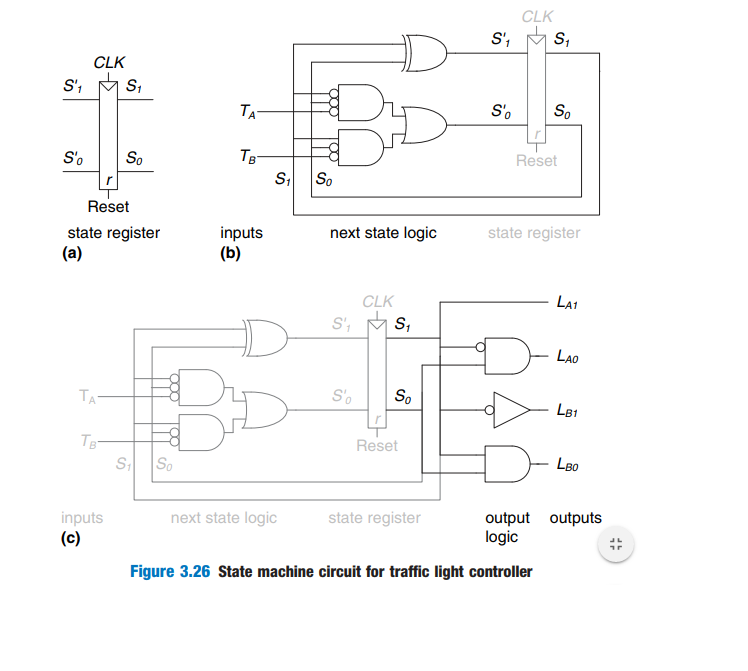

Consider the Cyclone IV LE shown in Figure 5.58. According to the datasheet, it has the timing specifications given in Table 5.5.(a) What is the minimum number of Cyclone IV LEs required to implement the FSM of Figure 3.26?(b) Without clock skew, what is the fastest clock frequency at which this FSM will run reliably?(c) With 3 ns of clock skew, what is the fastest frequency at which the FSM will run reliably??

CLK S', S, CLK S', S, TA S'. So S'o So TB Reset So Reset next state logic state register state register (a) inputs (b) CLK La1 S', S, LAO TA S'o So LB1 TB Reset LB0 So output outputs logic next state logic state register inputs (c) Figure 3.26 State machine circuit for traffic light controller S,

Step by Step Solution

3.42 Rating (165 Votes )

There are 3 Steps involved in it

a 5 LEs 2 for next state logic and state registers 3 for ... View full answer

Get step-by-step solutions from verified subject matter experts