Question: Repeat Exercise 23.11 with the double buffer of Figure 23.11 and the VHDL of Figure 23.12. The fail signal should propagate by only one stage

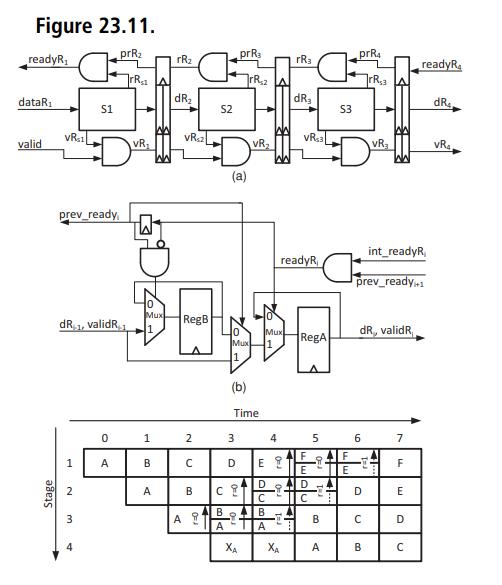

Repeat Exercise 23.11 with the double buffer of Figure 23.11 and the VHDL of Figure 23.12. The fail signal should propagate by only one stage per cycle (like the ready signal).

Data in Exercise 23.11

In Section 22.6.2 we briefly discussed speculation, where a downstream pipeline stage can trigger all upstream stages to drop their current problem. Add a fail signal into the block diagram of Figure 23.9 and the VHDL of Figure 23.10. When asserted, all upstream data should be invalidated.

Figure 23.11. prR readyR dataR valid Stage VR1 prev_ready 1 dR, validR 2 S1 3 4 D 0 rRA A VR 1 B rR A dR VR2 Mux DO RegB 1 A S2 2 AR prR D (a) B C rR2 Mux (b) Time 3 4 C DE? AD VR B -9. A DUBA ++ Mux 1 readyR 0: r=1 rR3 dR VR$3 7 RegA F E alalm 5 02 D C 1 B rat HL. XA A S3 F E prR 6 int_readyR, prev_ready+1 dR, validR I=. D rR,3 C VR B 7 F E D readyR C dR VR

Step by Step Solution

3.40 Rating (159 Votes )

There are 3 Steps involved in it

Get step-by-step solutions from verified subject matter experts