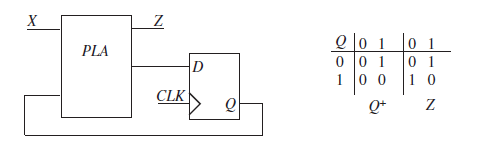

A sequential circuit consists of a PLA and a D flip-flop, as shown in the following diagram.

Question:

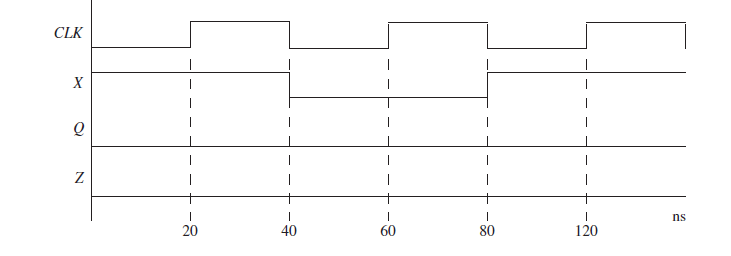

(a) Complete the timing diagram assuming that the propagation delay for the PLA is in the range 5 to 10 ns and the propagation delay from clock to output of the D flip-flop is 5 to 10 ns. Use cross-hatching on your timing diagram to indicate the intervals in which Q and Z can change, taking the range of propagation delays into account.

(b) Assuming that X always changes at the same time as the falling edge of the clock, what is the maximum setup and hold time specification that the flipflop can have and still maintain proper operation of the circuit?

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted: