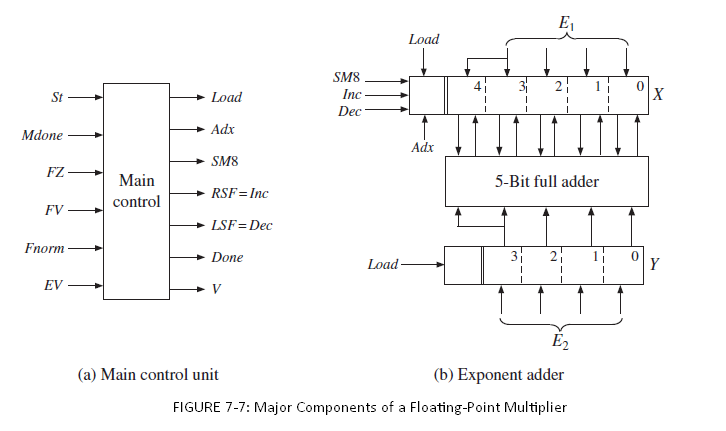

Redesign the floating-point multiplier in Figure 7. 7 using a common 5-bit full adder connected to a

Question:

(a) Redraw the block diagram, being sure to include the connections to the bus, and include all control signals.

(b) Draw a new SM chart for the new control.

(c) Write the Verilog description for the multiplier or specify the changes that need to be made to an existing description.

Transcribed Image Text:

E1 Load SM8 2 Inc- St Load Dec Adx Mdone Adx SM8 FZ Main 5-Bit full adder RSF=Inc control FV LSF= Dec Fnorm 3 2 Done Load EV E2 (a) Main control unit (b) Exponent adder FIGURE 7-7: Major Components of a Floating-Point Multiplier 4.

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 80% (10 reviews)

a b SM chart is similar to Figure 78 with added states for loading c define M B 0 module Prob711 CLK St Input Fout Eout V Done input CLK St input 3 0 ...View the full answer

Answered By

Rinki Devi

Professional, Experienced, and Expert tutor who will provide speedy and to-the-point solutions.

Hi there! Are you looking for a committed, reliable, and enthusiastic tutor? Well, teaching and learning are more of a second nature to me, having been raised by parents who are both teachers. I have done plenty of studying and lots of learning on many exciting and challenging topics. All these experiences have influenced my decision to take on the teaching role in various capacities. As a tutor, I am looking forward to getting to understand your needs and helping you achieve your academic goals. I'm highly flexible and contactable. I am available to work on short notice since I only prefer to work with very small and select groups of students.

I have been teaching students for 5 years now in different subjects and it's truly been one of the most rewarding experiences of my life. I have also done one-to-one tutoring with 100+ students and helped them achieve great subject knowledge.

5.00+

2+ Reviews

10+ Question Solved

Related Book For

Digital Systems Design Using Verilog

ISBN: 978-1285051079

1st edition

Authors: Charles Roth, Lizy K. John, Byeong Kil Lee

Question Posted:

Students also viewed these Sciences questions

-

(a) Draw a block diagram for a floating-point subtracter. Assume that the inputs to the subtracter are properly normalized, and the answer should be properly normalized. The fractions are 8 bits...

-

A description of a 74194 4-bit bidirectional shift register follows. The CLRb input is asynchronous and active low and overrides all the other control inputs. All other state changes occur following...

-

(a) Draw the block diagram for a divider that divides an 8-bit dividend by a 5-bit divisor to give a 3-bit quotient. The dividend register should be loaded when St = 1. (b) Draw an SM chart for the...

-

Question 5 [ 4 points ] In the table shown below is accounting equation information as it applies to Second Time Around Clothing. Calculate the missing amounts assuming that a . Assets decreased by $...

-

The following amounts were taken from the accounting records of May 31, 20Y7. Hargrove Services began its operations on June 1, of Hargrove Services, Inc., as 1, 20Y6. Capital...

-

An eight-station rotary indexing machine performs the machining operations shown in the accompanying table, together with processing times and breakdown frequencies for each station. The transfer...

-

15-9. Cul es la diferencia principal entre el canal de marketing y la cadena de suministro ?

-

Medical Dispensary borrowed $390,000 on January 2, 2012, by issuing a 10% serial bond payable that must be paid in three equal annual installments plus interest for the year. The first payment of...

-

Ivanhoe Company uses a perpetual inventory system and reports the following inventory transactions for the month of July: Units Unit Cost Total Cost July 1 Inventory 150 $13.00 $1,950.00 12 Purchases...

-

Harry is a stay-at-home father taking care of his two children. When he is not changing diapers or doing laundry, he can work online up to 18 hours in a day. Denote the number of hours he works by x....

-

This problem concerns the design of a circuit to find the square of a floating-point number, F x 2 E . F is a normalized 5-bit fraction, and E is a 5-bit integer; negative numbers are represented in...

-

A floating-point number system uses a 4-bit fraction and a 4-bit exponent with negative numbers expressed in 2s complement. Design an efficient system that will multiply the number by -4 (minus...

-

ProChem, Inc., produces chemicals for large biotech companies. It has the following data for manufacturing overhead costs during August 2017: ___________________________________ Variable ___________...

-

In this Capstone experience, you will develop a strategy playbook for a selected organization. You may be familiar with the concept of a playbook as it relates to a sports team, but what might that...

-

On January 1, 2024, the general ledger of Big Blast Fireworks includes the following account balances: Accounts Cash Debit Credit $25,900 Accounts Receivable 46,500 Allowance for Uncollectible...

-

The WRX can travel 1 / 4 of a mile in 1 3 . 9 sec . Calculate the acceleration over this distance if assumed constant.

-

You are expected to develop two simulators mimicking the behavior and analyze the performance of iterative multiplication algorithm and add-and-shift multiplication algorithm. You are free to use any...

-

A.BRK Company, which Manufactures bags, has a Capacity of 130,000 bags per month. Currently its operating capacity is 100,000 units. The company receives a special order of 20,000 bags at $9 a bag. A...

-

The following accounts appear in an adjusted trial balance of F-18 Consulting. Indicate whether each account would be reported in the (a) current asset; (b) property, plant, and equipment; (c)...

-

When is the indirect pattern appropriate, and what are the benefits of using it?

-

Predict the products for each of the following Diels-Alder reactions: (a) (b) (c) (d) (e) (f) . C CN

-

Predict the products for each of the following Diels-Alder reactions: (a) (b) (c) (d) (e) (f) HOOC, . COOH

-

Identify the reagents you would use to prepare each of the following compounds via a Diels-Alder reaction: (a) (b) (c) (d) (e) (f) (g) (h) COOH COOH

-

! Required information [ The following information applies to the questions displayed below. ] Year 1 total cash dividends Year 2 total cash dividends Year 3 total cash dividends Year 4 total cash...

-

Built-Tight is preparing its master budget for the quarter ended September 30, 2015. Budgeted sales and cash payments for product costs for the quarter follow: July August September Budgeted sales $...

-

inepired. 2. Suppliei on hard at the eind of the month tedaled $16800. 2 The balance in Prepaid Rent represucks 4 months of rent coves. 5. Desreciationet bullines is $5060 per vear

Study smarter with the SolutionInn App