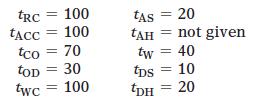

Question: A certain static RAM has the following timing parameters (in nanoseconds): (a) How long after the address lines stabilize will valid data appear at the

A certain static RAM has the following timing parameters (in nanoseconds):

(a) How long after the address lines stabilize will valid data appear at the outputs during a read cycle?

(b) How long will output data remain valid after C̅S̅ returns HIGH?

(c) How many read operations can be performed per second?

(d) How long should WE and C̅S̅ be kept HIGH after the new address stabilizes during a write cycle?

(e) What is the minimum time that input data must remain valid for a reliable write operation to occur?

(f) How long must the address inputs remain stable after W̅E̅ and C̅S̅ return HIGH?

(g) How many write operations can be performed per second?

100 TRC tAcc 100 = tco : 70 = 30 toD twc 100 = = tas = 20 TAH = not given tw = 40 tps 10 tDH 20 = =

Step by Step Solution

3.48 Rating (158 Votes )

There are 3 Steps involved in it

a How long after the address lines stabilize will valid data appear at the outputs during a read cycle The time it takes for valid data to appear at t... View full answer

Get step-by-step solutions from verified subject matter experts