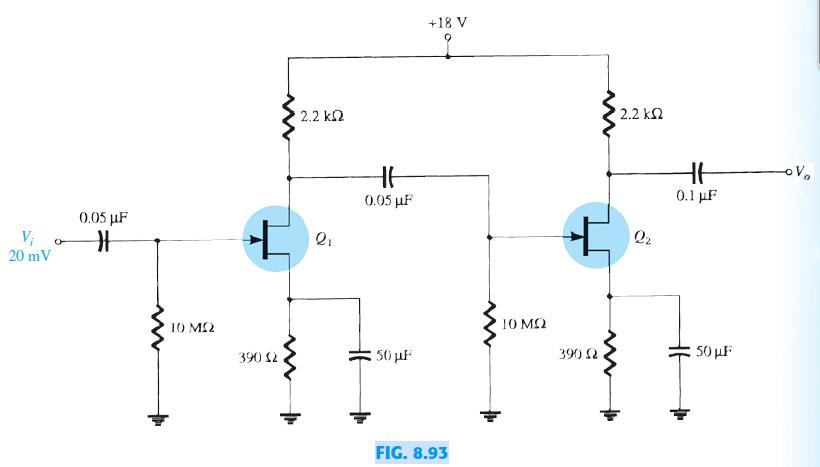

For the JFET cascade amplifier in Fig. 8.93 , calculate the dc bias conditions for the two

Question:

For the JFET cascade amplifier in Fig. 8.93 , calculate the dc bias conditions for the two identical stages, using JFETs with IDSS = 8 mA and VP = -4.5 V.

Transcribed Image Text:

+18 V 2.2 k2 2.2 k2 0.05 µF 0.1 µF 0.05 µF Q2 20 mV 10 M2 10 MQ 390 2 50 µF 390 2 50 µF FIG. 8.93

Fantastic news! We've Found the answer you've been seeking!

Step by Step Answer:

Answer rating: 72% (11 reviews)

For the JFET cascade amplifier in Fig 893 calculate the dc bias conditions for the two identical sta...View the full answer

Answered By

Labindao Antoque

I graduated in 2018 with a Bachelor of Science degree in Psychology from Dalubhasaan ng Lungsod ng San Pablo. I tutored students in classes and out of classes. I use a variety of strategies to tutor students that include: lecture, discussions about the subject matter, problem solving examples using the principles of the subject matter being discussed in class , homework assignments that are directed towards reinforcing what we learn in class , and detailed practice problems help students to master a concept. I also do thorough research on Internet resources or textbooks so that I know what students need to learn in order to master what is being taught in class .

0.00

0 Reviews

10+ Question Solved

Related Book For

Electronic Devices And Circuit Theory

ISBN: 9781292025636

11th Edition

Authors: Robert Boylestad, Louis Nashelsky

Question Posted:

Students also viewed these Engineering questions

-

Using IDSS = 9 mA and VP = -3 V for the characteristics of Fig. 6.25, calculate ID at VGS = -1 V using Shockley's equation and compare to the level in Fig. 6.25.

-

For the BJT cascade amplifier of Fig. 5.176, calculate the dc bias voltages and collector current for each stage. +15 V 5.1 kQ 24 k 5.1 k 24 k2 0.5 HF If 0.5 pF - 150 6.2 k2 6.2 kQ 50 uF

-

Using an average value of 2.9 mA for the IDSS of the 2N3797 MOSFET of Fig. 6.34, determine the level of VGS that will result in a maximum drain current of 20 mA if VP = -5 V.

-

Identify each process as endothermic or exothermic and indicate the sign of H. (a) Sweat evaporating from skin (b) Water freezing in a freezer (c) Wood burning in a fire

-

In the United States, say gasoline costs consumers about $2.50 per gallon. In Italy, say it costs consumers about $6 per gallon. What effect does this price differential likely have on a. The size of...

-

Refer to the information in PA12-2. Required: Prepare the cash flows from operating activities section of the 2013 statement of cash flows using the directmethod. Income Statement Selected Balance...

-

oyles law Refer to Exercise 32. We took the logarithm (base 10) of the values for both variables. Some computer output from a linear regression analysis on the transformed data is shown below....

-

The Duncan Companys stock is currently selling for $15. People generally expect its price to rise to $18 by the end of next year. They also expect that it will pay a dividend of $.50 per share during...

-

Way Cool produces two different models of air conditioners. The company produces the mechanical systems in its components department. The mechanical systems are combined with the housing assembly in...

-

Imax Corporation is a large entertainment technology company, with headquarters in New York and Toronto, and theatres worldwide. Its share price, which was as high as Can.$ 13.89 on the Toronto Stock...

-

If both JFETs in the cascade amplifier of Fig. 8.93 are changed to those having specifications I DSS = 12 mA and V P = -3 V, calculate the resulting d c bias of each stage. Fig. 8.93 +18 V 2.2 k2 2.2...

-

For the common-gate configuration of Fig. 8.92 : a. Determine A vNL , Z i and Z o . b. Sketch the two-port model of Fig. 5.75 with the parameters determined in part (a) in place. c. Determine A vL...

-

What role does the normal probability plot play in examining whether the multiple regression model is appropriate for a given set of data?

-

What volumetric airflow rate (Qa) is required to maintain a G value of 500s-1 in a basin that is 2.75 m deep and provides a liquid detention time of 5 min? Perform the exercise for water temperatures...

-

Read this article, then answer the following questions: 1- Description of Instrument: a. Title of instrument, author(s), publication date 2/18/24, 5:43 PM Abuse Risk Inventory for Women: EBSCOhost...

-

Suppose that there is a magnetic field B(x, y, z) = x2 filling a 3D space. The coordinates are set up as a Cartesian coordinate system with = 2. For all the discussions below, ignore the units. a)...

-

A vertical solid cylinder of uniform cross-sectional area A floats in water. The cylinder is partially submerged. When the cylinder floats at rest, a mark is aligned with the water surface. The...

-

Non-manufacturing fixed cost for year 2011 equal to:$60,780 out of which half are Administrative expenses.Administrative expenses are expected to increase by: 10%The total Variable nonmanufacturing...

-

An item has a weekly demand of 240 units throughout the year. The item has a unit value of $42 and the company uses 20% of the item value for the annual inventory cost. When ordered, the setup cost...

-

a. Why does the Wi-Fi Alliance release compatibility testing profiles in waves instead of combining the entire standards features initially? 27a1.) An 802.11ac Wi-Fi compatibility testing profile...

-

The efficiency of a gas chromatography column is measured by a parameter called plate height (H, mm) which is related to the gas flow rate (u, mL/min) by the van Deemter equation: H = A + B/u + Cu,...

-

Write each answer with a reasonable number of figures. Find the absolute and percent relative uncertainty for each answer. (a) [12.41 (0.09) 4.16 ( 0.01)] 7.068 2 ( 0.000 4) = ? (b) [3.26 (0.10) ...

-

How many milliliters of 53.4 (0.4) wt% NaOH with a density of 1.52 ( 0.01) g/mL will you need to prepare 2.000 L of 0.169 M NaOH? (b) If the uncertainty in delivering NaOH is [1] 0.01 mL, calculate...

-

The following information is provided by Garden Gears for a new product it recently introduced: Total unit cost $50 Desired ROI per unit $22 Target selling price $72 How much is Garden Gears'...

-

Solid bank loan P5 million to a borrower on January 1, 2018. The terms of the loan require principal payments of P1 million each year for five years plus interest at 8%. The first principal and...

-

3) Assuming annual sales of $250,000 and a 50% gross (contribution) margin, calculate the following a. Average collection period if ending receivables total $45,000 b. Ending days-on-hand of...

Study smarter with the SolutionInn App