Question: Design a four-bit synchronous counter with parallel load. Use T flip-flops, instead of the D flip-flops used in Section 5.9.3. Section 5.9.3 Counters with Parallel

Design a four-bit synchronous counter with parallel load. Use T flip-flops, instead of the D flip-flops used in Section 5.9.3.

Section 5.9.3

Counters with Parallel Load

Often it is necessary to start counting with the initial count being equal to 0. This state can be achieved by using the capability to clear the flip-flops as indicated in Figure 5.22. But sometimes it is desirable to start with a different count. To allow this mode of operation, a counter circuit must have some inputs through which the initial count can be loaded. Using the Clear and Preset inputs for this purpose is a possibility, but a better approach is discussed below.

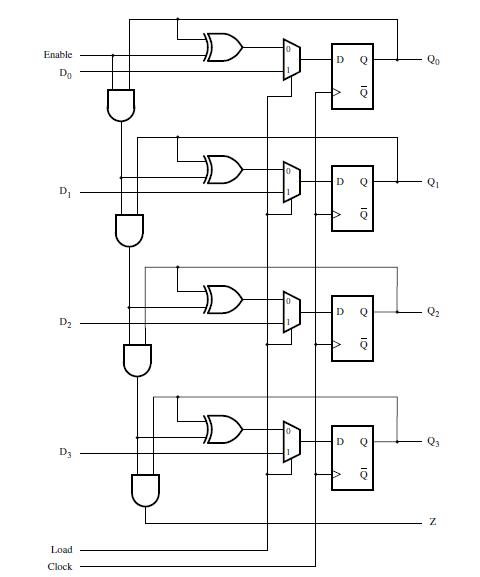

The circuit of Figure 5.23 can be modified to provide the parallel-load capability as shown in Figure 5.24. A two-input multiplexer is inserted before each D input. One input to the multiplexer is used to provide the normal counting operation. The other input is a data bit that can be loaded directly into the flip-flop. A control input, Load, is used to choose the mode of operation. The circuit counts when Load = 0. A new initial value, D3D2D1D0, is loaded into the counter when Load = 1.

Enable Do D 2 2 Load Clock D D Q D D 10 Q 10 Q 10 D Q 10 & 2 N

Step by Step Solution

3.19 Rating (166 Votes )

There are 3 Steps involved in it

Solution The design is as follows i For the design of 4bit counter the counter will ... View full answer

Get step-by-step solutions from verified subject matter experts