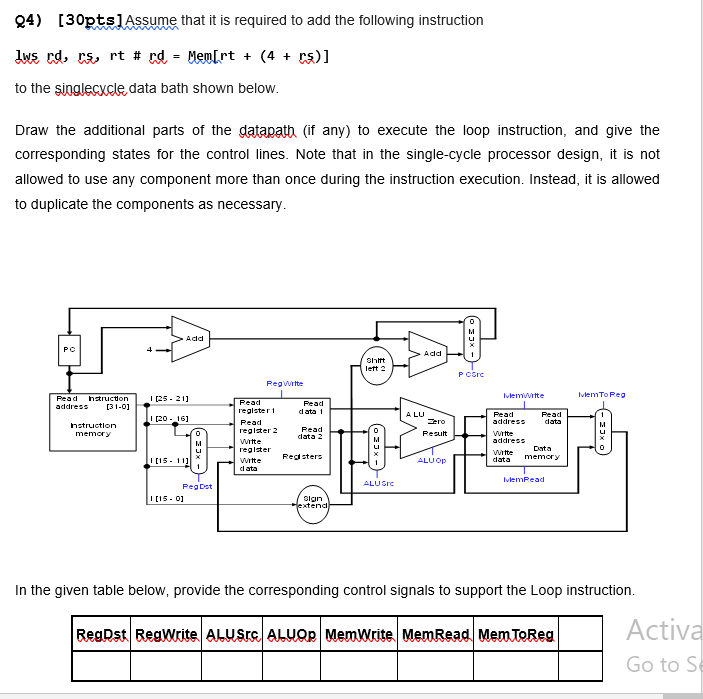

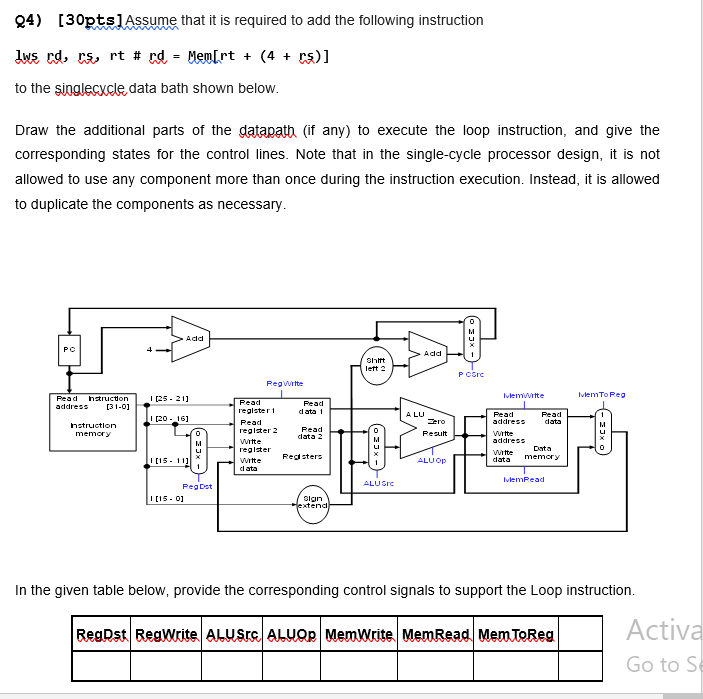

04) [30pts] Assume that it is required to add the following instruction lws rd, rs, rt # rd = Mem[rt + (4 + rs)] to the singlecycle data bath shown below. Draw the additional parts of the datapath (if any) to execute the loop instruction, and give the corresponding states for the control lines. Note that in the single-cycle processor design, it is not allowed to use any component more than once during the instruction execution. Instead, it is allowed to duplicate the components as necessary. Aca PC Add Shirt left 2 POSIC Peg Witte 1 [25.21] Ivlem witte Pead Instruction address [31-0) Item To Reg Peach data 1 [2016] Instruction memory Read register Read register 2 Witte register Witte data ALU Zero Pesuit Pead data 2 Pead Pead address data Witte address Data Witte data memory O XCEH II 11 [15.11) Registers ALU OP ALUST IviemRead Pegast 1 [15.01 sign extendi In the given table below, provide the corresponding control signals to support the Loop instruction. Regnst RegWrite ALUSIS ALUOP MemWrite MemRead Mem ToReg Activa Go to S 04) [30pts] Assume that it is required to add the following instruction lws rd, rs, rt # rd = Mem[rt + (4 + rs)] to the singlecycle data bath shown below. Draw the additional parts of the datapath (if any) to execute the loop instruction, and give the corresponding states for the control lines. Note that in the single-cycle processor design, it is not allowed to use any component more than once during the instruction execution. Instead, it is allowed to duplicate the components as necessary. Aca PC Add Shirt left 2 POSIC Peg Witte 1 [25.21] Ivlem witte Pead Instruction address [31-0) Item To Reg Peach data 1 [2016] Instruction memory Read register Read register 2 Witte register Witte data ALU Zero Pesuit Pead data 2 Pead Pead address data Witte address Data Witte data memory O XCEH II 11 [15.11) Registers ALU OP ALUST IviemRead Pegast 1 [15.01 sign extendi In the given table below, provide the corresponding control signals to support the Loop instruction. Regnst RegWrite ALUSIS ALUOP MemWrite MemRead Mem ToReg Activa Go to S