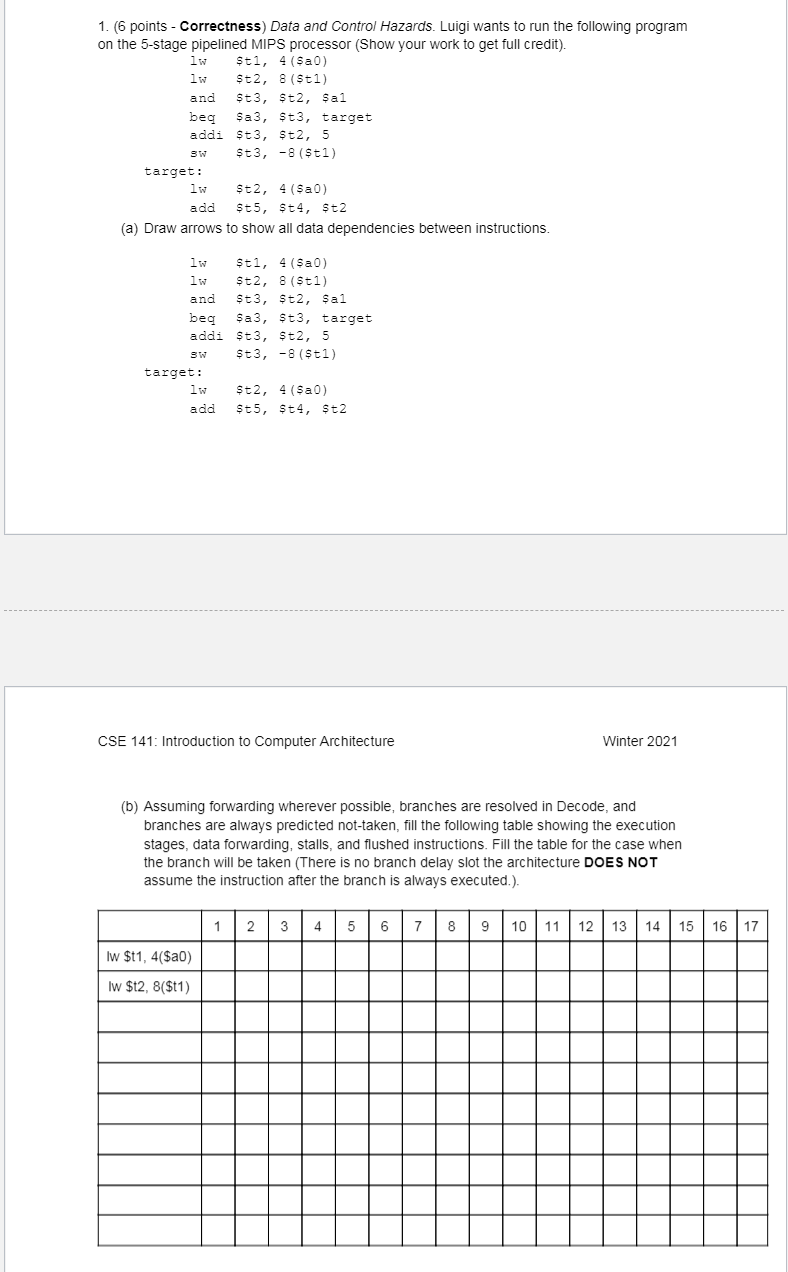

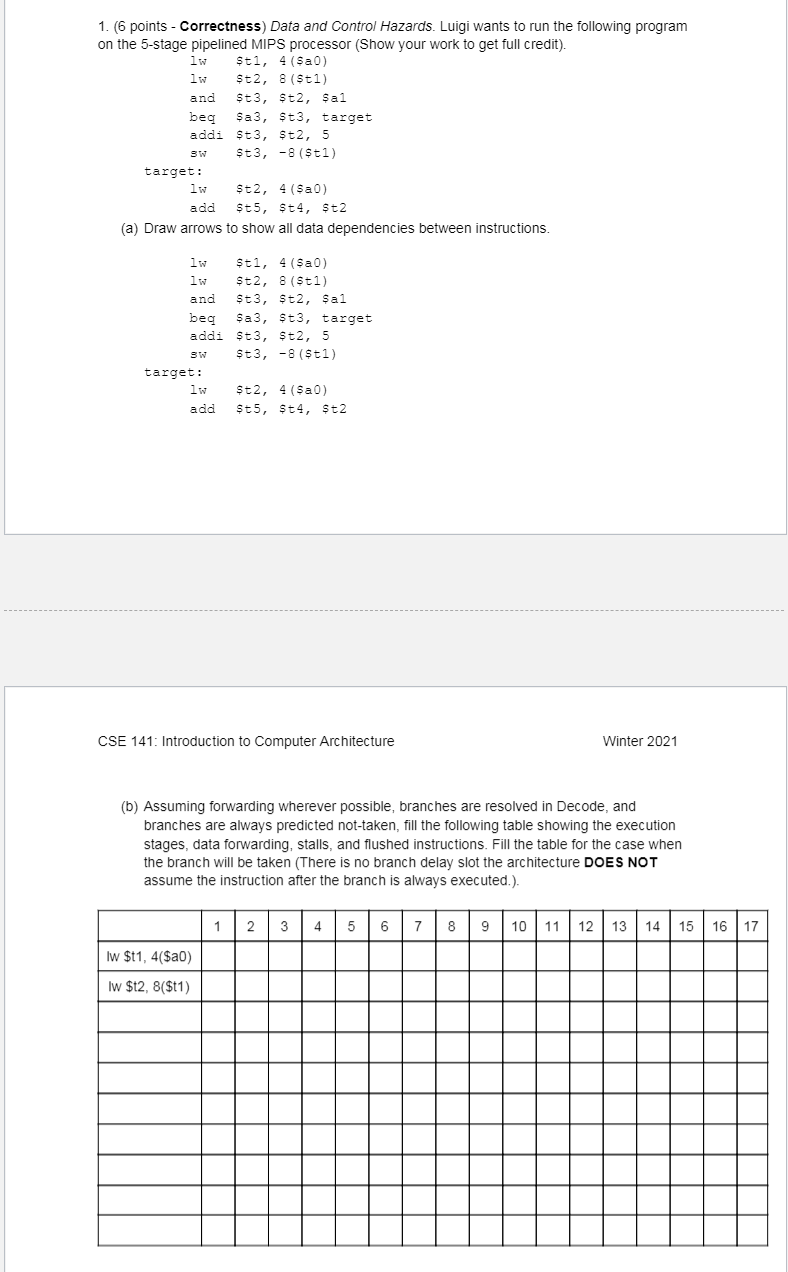

1. (6 points - Correctness) Data and Control Hazards. Luigi wants to run the following program on the 5-stage pipelined MIPS processor (Show your work to get full credit). lw Sti, 4 (Sa) lw St2, 8 (Sti) and St3, $t2, $al beg Sa3, St3, target addi $t3, $t2, 5 sw $t3, -8 ($t1) target: 1w St2, 4 (Sa0) add St5, $t4, $t2 (a) Draw arrows to show all data dependencies between instructions. lw $ti, 4 (Sa) lw st2, 3 (51) and St3, St2, Sal beg $a3, $t3, target addi $t3, $t2, 5 3w $t3, -8 ($t1) target: lw 12, 4 (20) add St5, $t4, $t2 CSE 141: Introduction to Computer Architecture Winter 2021 (b) Assuming forwarding wherever possible, branches are resolved in Decode, and branches are always predicted not-taken, fill the following table showing the execution stages, data forwarding, stalls, and flushed instructions. Fill the table for the case when the branch will be taken (There is no branch delay slot the architecture DOES NOT assume the instruction after the branch is always executed.). 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 lw $t1, 4($a0) lw $t2, 8($t1) 1. (6 points - Correctness) Data and Control Hazards. Luigi wants to run the following program on the 5-stage pipelined MIPS processor (Show your work to get full credit). lw Sti, 4 (Sa) lw St2, 8 (Sti) and St3, $t2, $al beg Sa3, St3, target addi $t3, $t2, 5 sw $t3, -8 ($t1) target: 1w St2, 4 (Sa0) add St5, $t4, $t2 (a) Draw arrows to show all data dependencies between instructions. lw $ti, 4 (Sa) lw st2, 3 (51) and St3, St2, Sal beg $a3, $t3, target addi $t3, $t2, 5 3w $t3, -8 ($t1) target: lw 12, 4 (20) add St5, $t4, $t2 CSE 141: Introduction to Computer Architecture Winter 2021 (b) Assuming forwarding wherever possible, branches are resolved in Decode, and branches are always predicted not-taken, fill the following table showing the execution stages, data forwarding, stalls, and flushed instructions. Fill the table for the case when the branch will be taken (There is no branch delay slot the architecture DOES NOT assume the instruction after the branch is always executed.). 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 lw $t1, 4($a0) lw $t2, 8($t1)