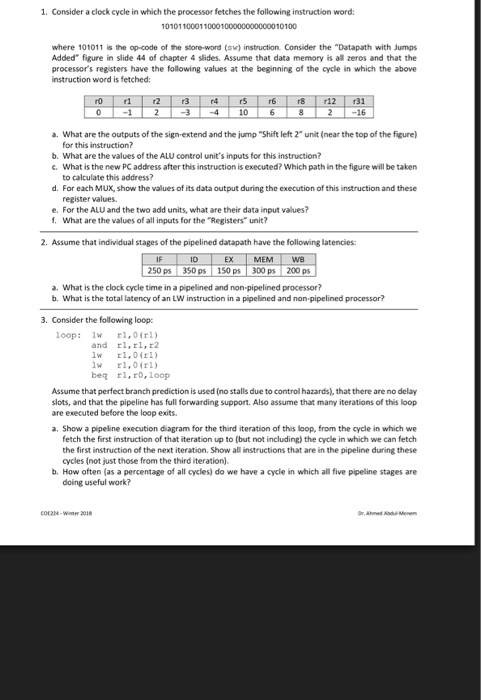

1. Consider a clock cycle in which the processor fetches the following instruction word: 10101100011000100000000000010100 where 101011 the op-code of the store-word (sw) instruction Consider the "Datapath with Jumps Added" figure in slide 44 of chapter 4 slides. Assume that data memory is all zeros and that the processor's registers have the following values at the beginning of the cycle in which the above nstruction word is fetched: ro r6rt8 r31 16 r4 34 10 a. What are the outputs of the sign-extend and the jump "Shift left 2" unit (near the top of the figurel for this instruction? b. What are the values of the ALU control unit's inputs for this instruction? c. What is the new PC address after this instruction is executed? Which path in the figure will be takern to calculate this address? d. For each MUX, show the values of its data output during the execution of this instruction and these register values e. For the ALU and the two add units, what are their data input values? f. What are the values of all inputs for the "Registers unit? 2. Assume that individual stages of the pipelined datapath have the following latencies IF ID EX MEM WB 250 ps 350 ps 150 ps 300p 200 a. What is the clock cycle time in a pipelined and non-pipelined processor? b. What is the total latency of an LW instruction in a pipelined and non pipelined processor? 3. Consider the following loop: loop: 1 rl,0(rl) and rl,rl,r2 ,0(r1) rl,0(r1) beq rl,ro, loop Assume that perfect branch prediction is used (no stalls due to control hazards), that there are no delay slots, and that the pipeline has full forwarding support. Also assume that many iterations of this loop are executed before the loop exits. a. Show a pipeline execution diagram for the third iteration of this loop, from the cycle in which we fetch the first instruction of that iteration up to (but not including) the cycle in which we can fetch the first instruction of the next iteration. Show all instructions that are in the pipeline during these cycles (not just those from the third iteration. b. How often (as a percentage of all cycles) do we have a cycle in which all five pipeline stages are doing useful work