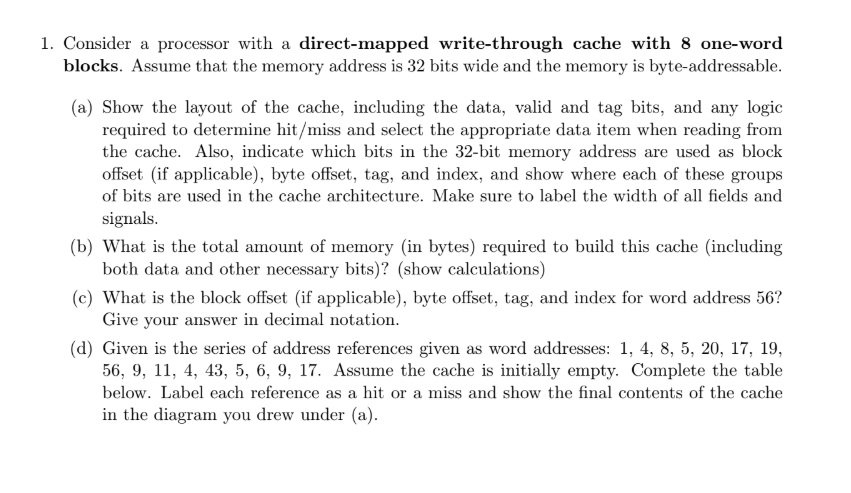

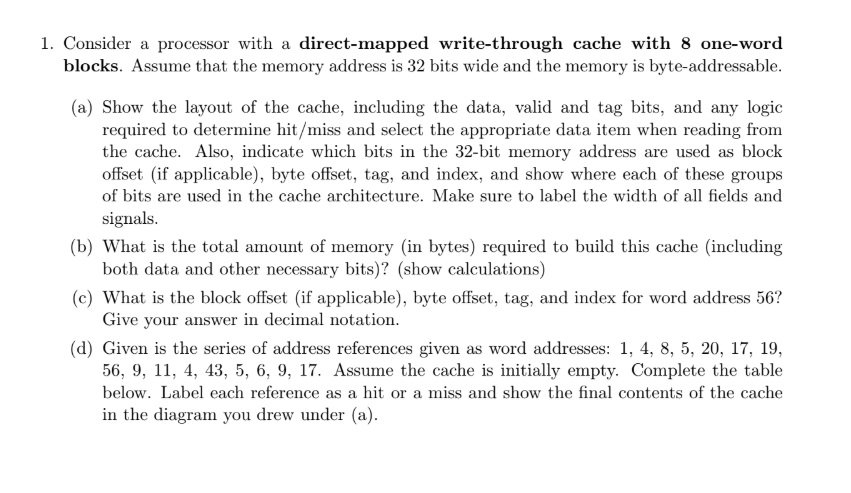

1. Consider a processor with a direct-mapped write-through cache with 8 one-word blocks. Assume that the memory address is 32 bits wide and the memory is byte-addressable (a) Show the layout of the cache, including the data, valid and tag bits, and any logic required to determine hit/miss and select the appropriate data item when reading from the cache. Also, indicate which bits in the 32-bit memory address are used as block offset (if applicable), byte offset, tag, and index, and show where each of these groups of bits are used in the cache architecture. Make sure to label the width of all fields and signals both data and other necessary bits)? (show calculations) Give your answer in decimal notation (b) What is the total amount of memory (in bytes) required to build this cache (including (c) What is the block offset (if applicable), byte offset, tag, and index for word address 56? (d) Given is the series of address references given as word addresses: 1, 4, 8, 5, 20, 17, 19, 56, 9, 11, 4, 43, 5, 6, 9, 17. Assume the cache is initially empty. Complete the table below. Label each reference as a hit or a miss and show the final contents of the cache in the diagram you drew under (a) 1. Consider a processor with a direct-mapped write-through cache with 8 one-word blocks. Assume that the memory address is 32 bits wide and the memory is byte-addressable (a) Show the layout of the cache, including the data, valid and tag bits, and any logic required to determine hit/miss and select the appropriate data item when reading from the cache. Also, indicate which bits in the 32-bit memory address are used as block offset (if applicable), byte offset, tag, and index, and show where each of these groups of bits are used in the cache architecture. Make sure to label the width of all fields and signals both data and other necessary bits)? (show calculations) Give your answer in decimal notation (b) What is the total amount of memory (in bytes) required to build this cache (including (c) What is the block offset (if applicable), byte offset, tag, and index for word address 56? (d) Given is the series of address references given as word addresses: 1, 4, 8, 5, 20, 17, 19, 56, 9, 11, 4, 43, 5, 6, 9, 17. Assume the cache is initially empty. Complete the table below. Label each reference as a hit or a miss and show the final contents of the cache in the diagram you drew under (a)