Answered step by step

Verified Expert Solution

Question

1 Approved Answer

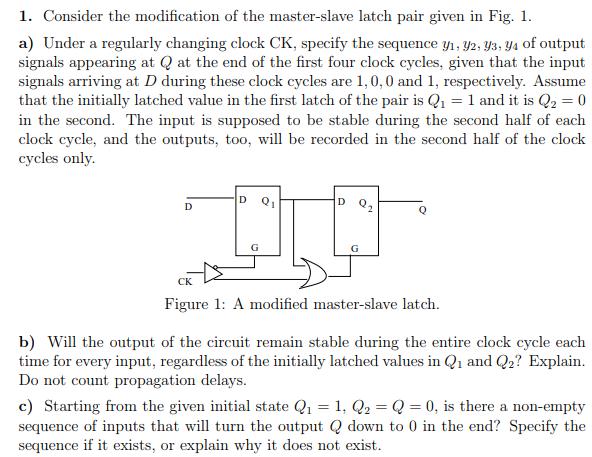

1. Consider the modification of the master-slave latch pair given in Fig. 1. a) Under a regularly changing clock CK, specify the sequence y1,

1. Consider the modification of the master-slave latch pair given in Fig. 1. a) Under a regularly changing clock CK, specify the sequence y1, 92, 93, 94 of output signals appearing at Q at the end of the first four clock cycles, given that the input signals arriving at D during these clock cycles are 1,0,0 and 1, respectively. Assume that the initially latched value in the first latch of the pair is Q = 1 and it is Q = 0 in the second. The input is supposed to be stable during the second half of each clock cycle, and the outputs, too, will be recorded in the second half of the clock cycles only. D D D G CK Figure 1: A modified master-slave latch. b) Will the output of the circuit remain stable during the entire clock cycle each time for every input, regardless of the initially latched values in Q1 and Q2? Explain. Do not count propagation delays. c) Starting from the given initial state Q = 1, Q2 = Q = 0, is there a non-empty sequence of inputs that will turn the output Q down to 0 in the end? Specify the sequence if it exists, or explain why it does not exist.

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started