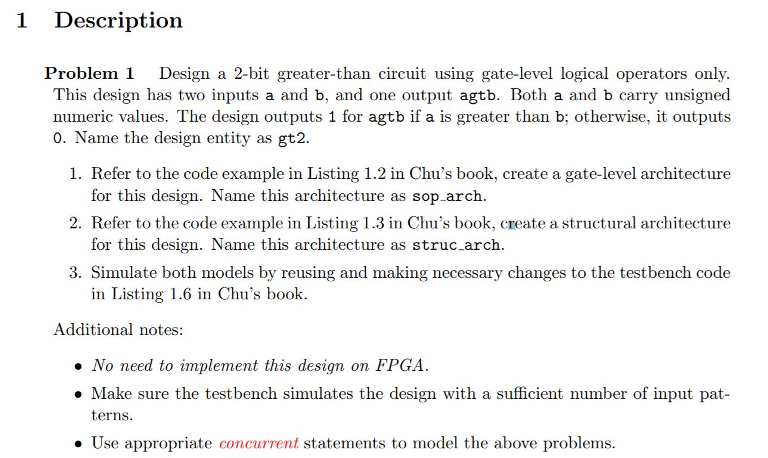

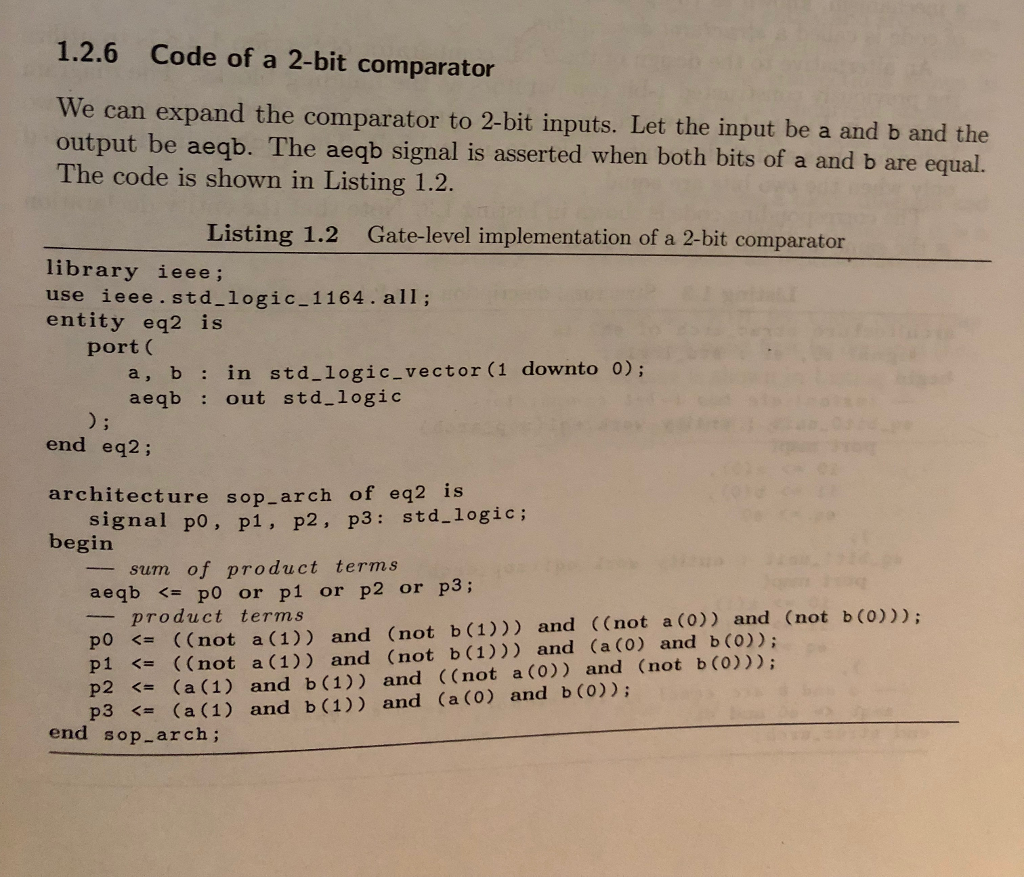

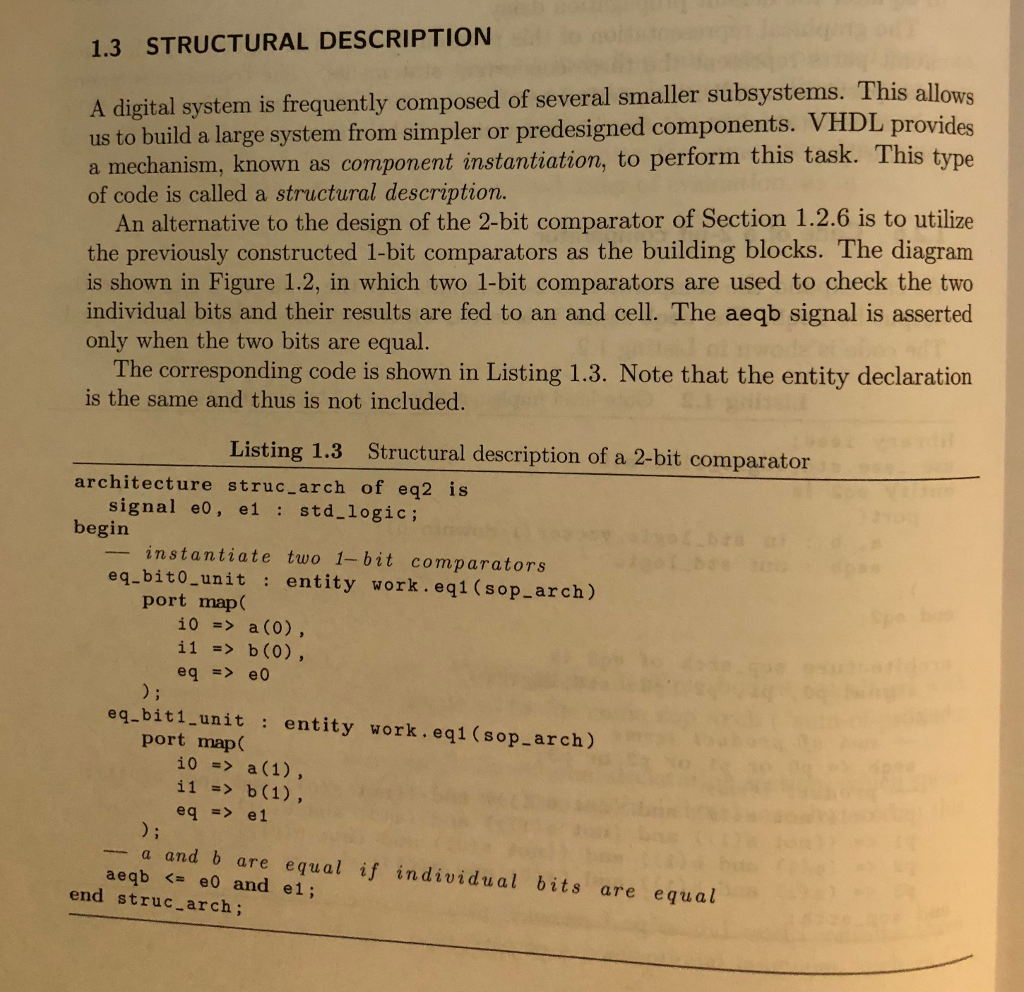

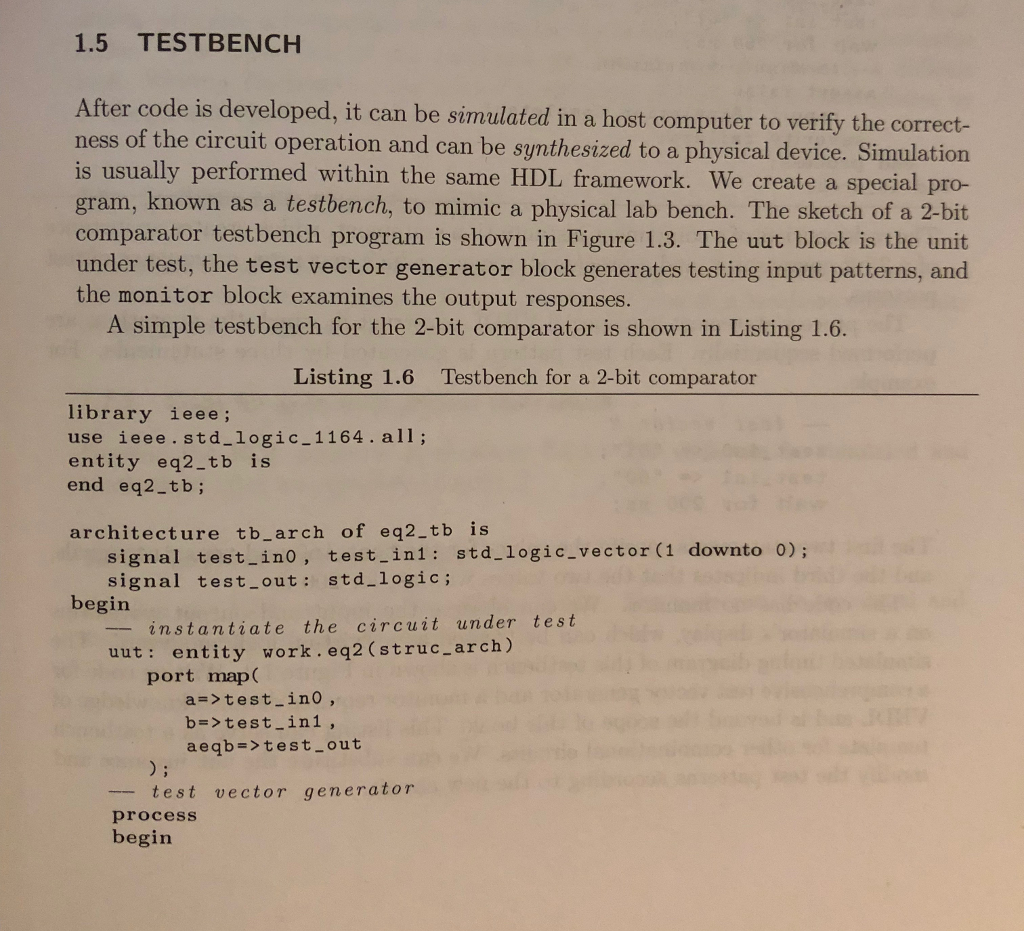

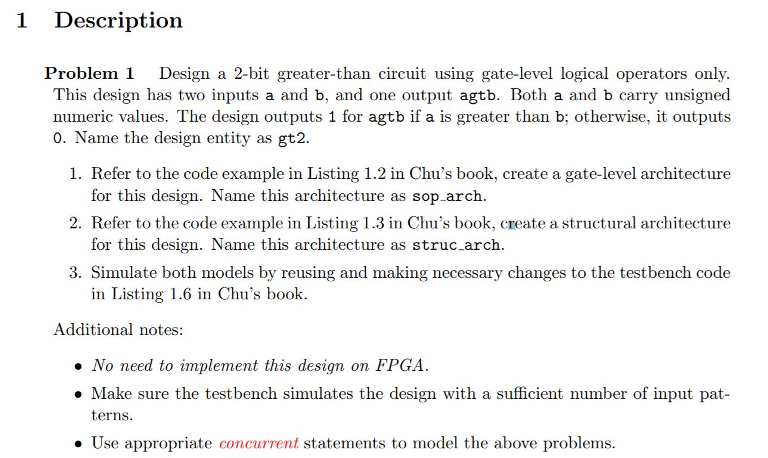

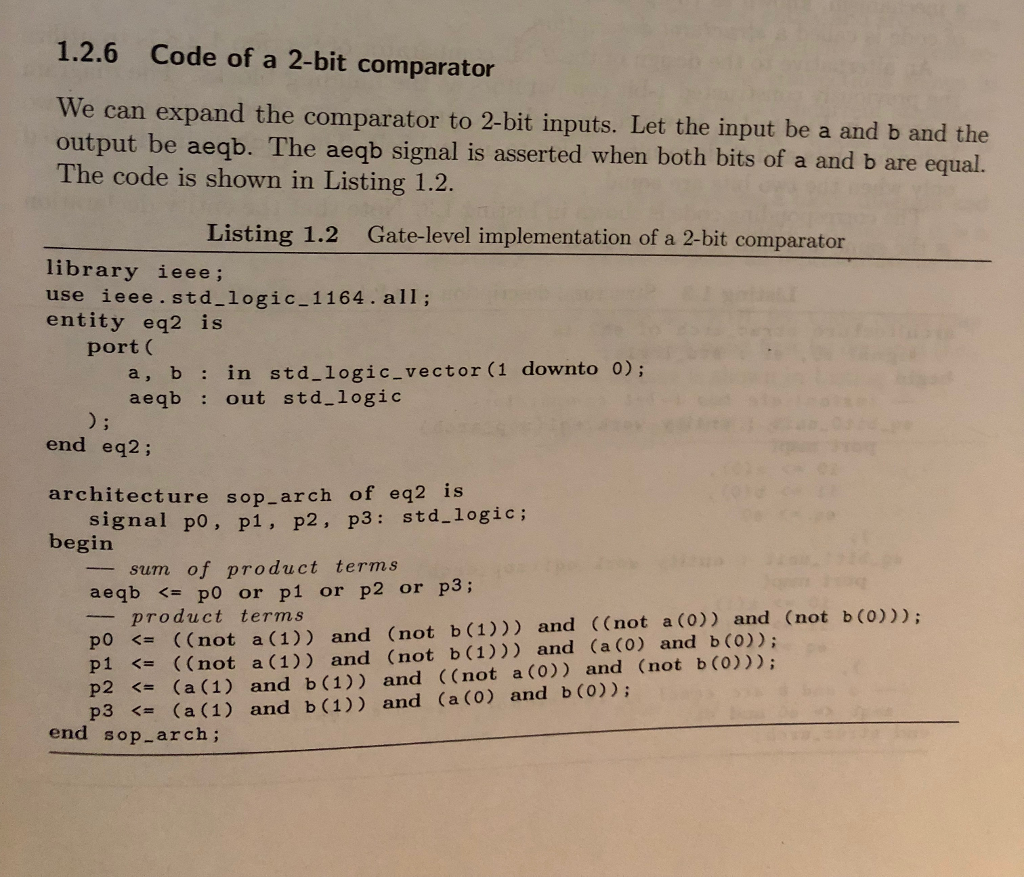

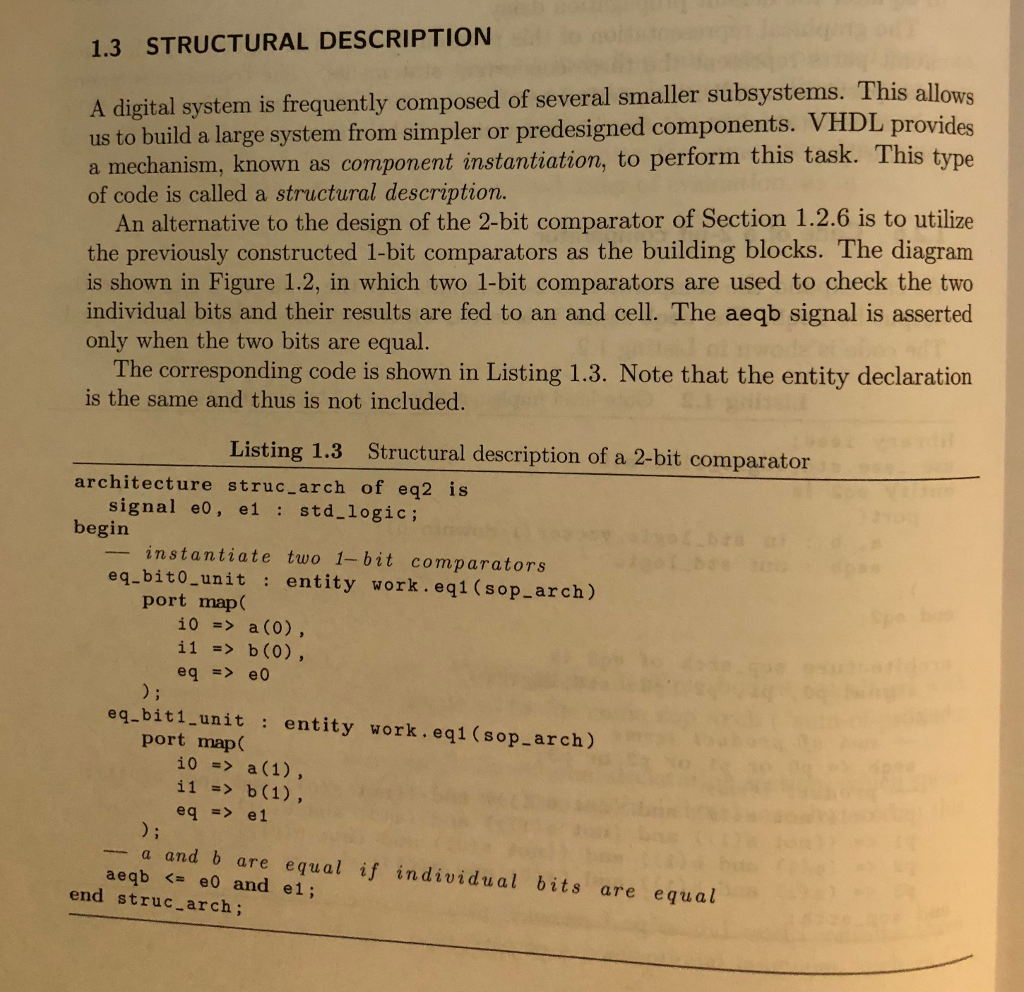

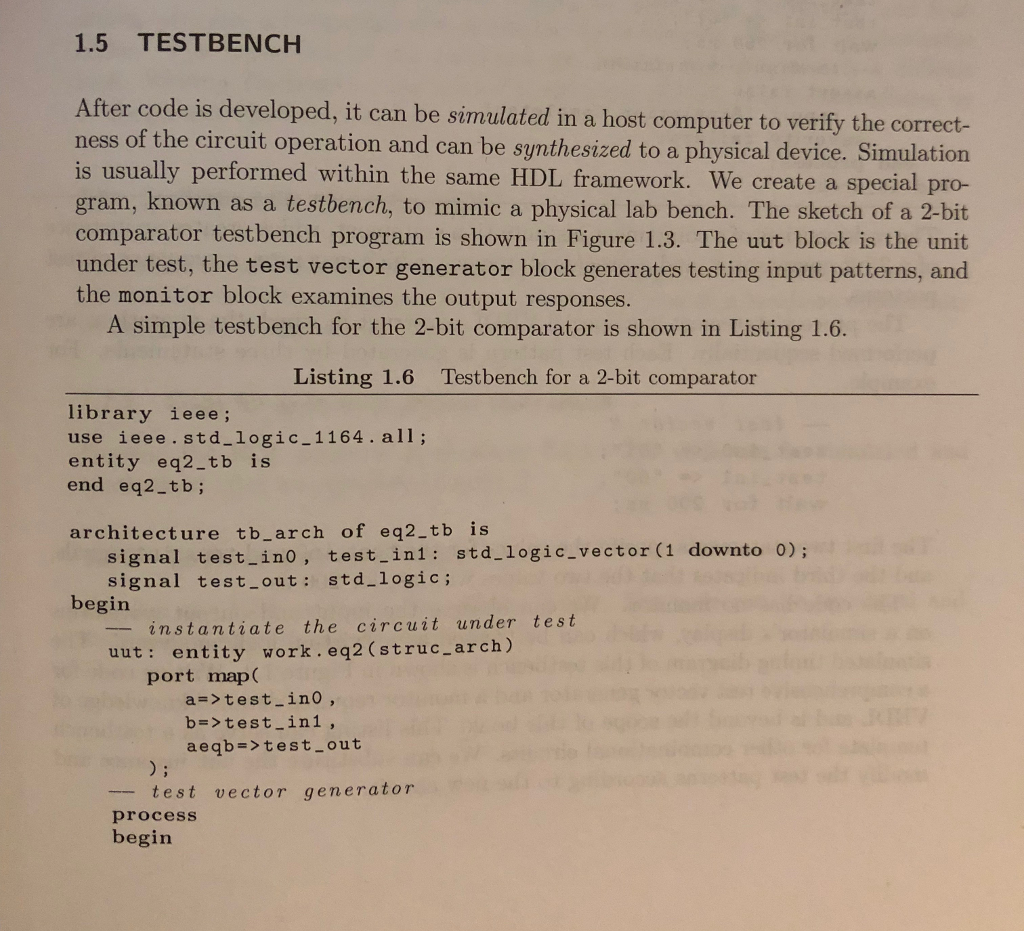

1 Description Problem 1 Design a 2-bit greater-than circuit using gate-level logical operators only. This design has two inputs a and b, and one output agtb. Both a and b carry unsigned numeric values. The design outputs 1 for agtb if a is greater than b; otherwise, it outputs 0. Name the design entity as gt2. 1. Refer to the code example in Listing 1.2 in Chu's book, create a gate-level architecture for this design. Name this architecture as sop_arch. 2. Refer to the code example in Listing 1.3 in Chu's book, create a structural architecture for this design. Name this architecture as struc_arch. 3. Simulate both models by reusing and making necessary changes to the testbench code in Listing 1.6 in Chu's book. Additional notes: No need to implement this design on FPGA. Make sure the testbench simulates the design with a sufficient number of input pat- terns. Use appropriate concurrent statements to model the above problems. 1.2.6 Code of a 2-bit comparator We can expand the comparator to 2-bit inputs. Let the input be a and b and the output be aeqb. The aeqb signal is asserted when both bits of a and b are equal. The code is shown in Listing 1.2. Listing 1.2 Gate-level implementation of a 2-bit comparator library ieee; use ieee.std_logic_1164. all; entity eq2 is port a, b: in std_logic_vector (1 downto 0); aeqb : out std_logic ); end eq2; architecture sop_arch of eq2 is signal po, p1, P2, P3: std_logic; begin -- sum of product terms aeqb a(0), i1 => b (0), eq => 0 ); eq-biti_unit : entity work.eqi (sop-arch) port map i0 => a (1), il => 6(1), eq => e1 a and b are equal if individual bits are equal aeqb testino, br>test_in1 , aeqb=>test_out test vector generator process begin 1 Description Problem 1 Design a 2-bit greater-than circuit using gate-level logical operators only. This design has two inputs a and b, and one output agtb. Both a and b carry unsigned numeric values. The design outputs 1 for agtb if a is greater than b; otherwise, it outputs 0. Name the design entity as gt2. 1. Refer to the code example in Listing 1.2 in Chu's book, create a gate-level architecture for this design. Name this architecture as sop_arch. 2. Refer to the code example in Listing 1.3 in Chu's book, create a structural architecture for this design. Name this architecture as struc_arch. 3. Simulate both models by reusing and making necessary changes to the testbench code in Listing 1.6 in Chu's book. Additional notes: No need to implement this design on FPGA. Make sure the testbench simulates the design with a sufficient number of input pat- terns. Use appropriate concurrent statements to model the above problems. 1.2.6 Code of a 2-bit comparator We can expand the comparator to 2-bit inputs. Let the input be a and b and the output be aeqb. The aeqb signal is asserted when both bits of a and b are equal. The code is shown in Listing 1.2. Listing 1.2 Gate-level implementation of a 2-bit comparator library ieee; use ieee.std_logic_1164. all; entity eq2 is port a, b: in std_logic_vector (1 downto 0); aeqb : out std_logic ); end eq2; architecture sop_arch of eq2 is signal po, p1, P2, P3: std_logic; begin -- sum of product terms aeqb a(0), i1 => b (0), eq => 0 ); eq-biti_unit : entity work.eqi (sop-arch) port map i0 => a (1), il => 6(1), eq => e1 a and b are equal if individual bits are equal aeqb testino, br>test_in1 , aeqb=>test_out test vector generator process begin