Answered step by step

Verified Expert Solution

Question

1 Approved Answer

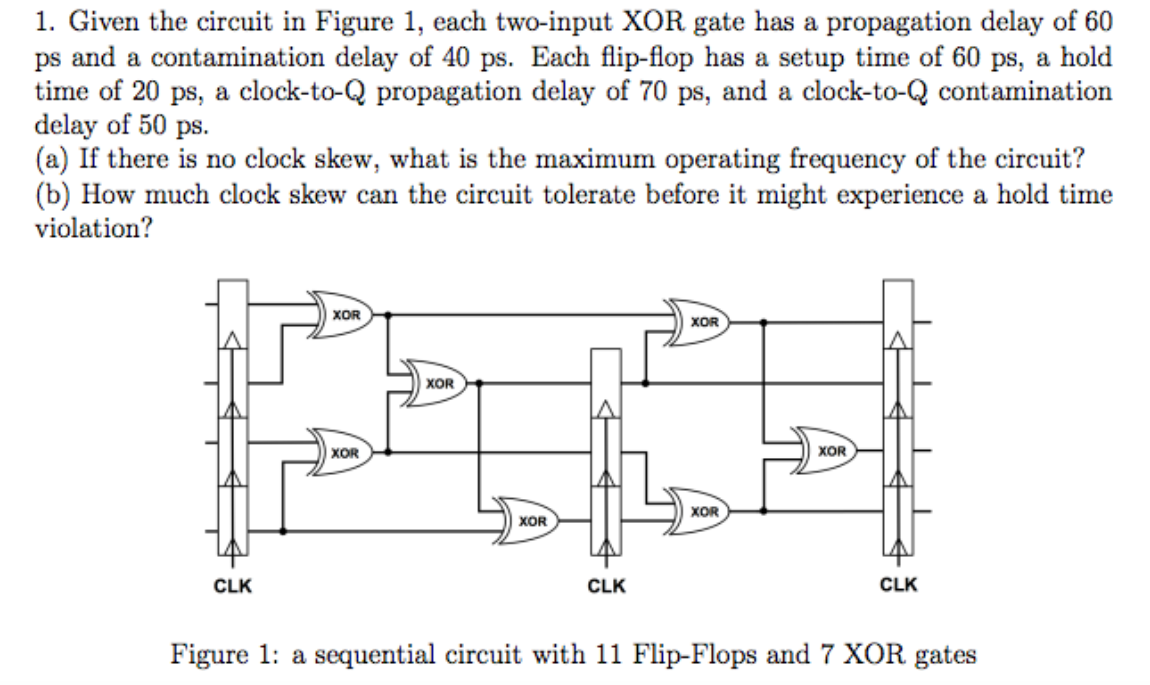

1. Given the circuit in Figure 1, each two-input XOR gate has a propagation delay of 60 ps and a contamination delay of 40 ps.

1. Given the circuit in Figure 1, each two-input XOR gate has a propagation delay of 60 ps and a contamination delay of 40 ps.

Each flip-flop has a setup time of 60 ps, a hold time of 20 ps, a clock-to-Q propagation delay of 70 ps, and a clock-to-Q contamination delay of 50 ps.

(a) If there is no clock skew, what is the maximum operating frequency of the circuit?

?(b) How much clock skew can the circuit tolerate before it might experience a hold time violation?

Please give explanation to help understand, thanks!

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started