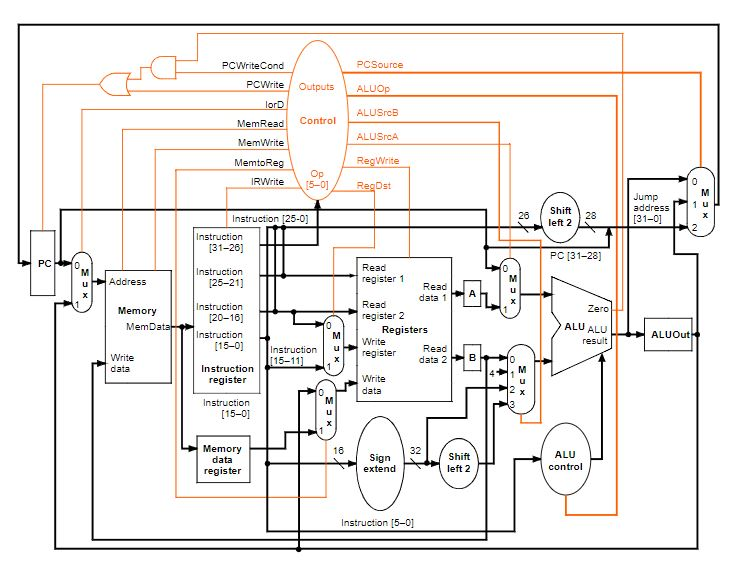

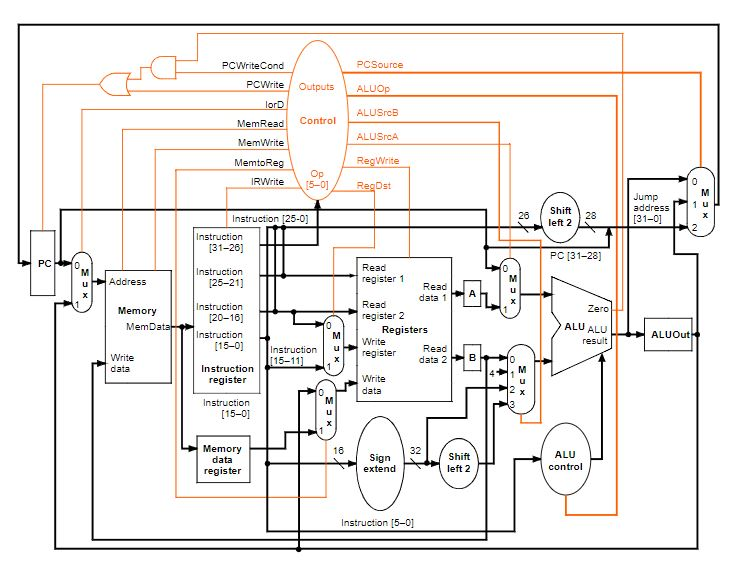

1. Modify the multicycle datapath to support the lui instruction. Recall that immediate values in MIPS are 16 bits whereas registers are 32 bits. So far in class, l of the immediate forms of MIPS instructions we have discussed correspond directly to the lower 16 bits of data, and the upper 16 bits are either sign-extended from the 16-bit immediate value or filled with zeros. However, the MIPS instruction set includes the load upper immediate instruction (lui) to allow the upper 16 bits of a register to be loaded directly from an immediate value. lui Srt, Offset is functionally equivalent to this sequence of familiar MIPS instructions (althoughlui is a single instruction) addi Srt, S0, offset s11 Srt, Srt, 16 You should implement lui so that it requires only 3 cycles, and the fetch cycle (state 0) should remain unchanged, (i.e., the instruction word is not available until after this first cycle). Do not modify the existing register file or ALU. Add any necessary components, connections, and control signals to the multicycle datapath (igure available from myCourses, which comes from Ed. 3, Fig. 5.28), and show the necessary modifications to the finite state machine diagram (available from myCourses, which comes from Ed. 3, Fig. 5.38). 1. Modify the multicycle datapath to support the lui instruction. Recall that immediate values in MIPS are 16 bits whereas registers are 32 bits. So far in class, l of the immediate forms of MIPS instructions we have discussed correspond directly to the lower 16 bits of data, and the upper 16 bits are either sign-extended from the 16-bit immediate value or filled with zeros. However, the MIPS instruction set includes the load upper immediate instruction (lui) to allow the upper 16 bits of a register to be loaded directly from an immediate value. lui Srt, Offset is functionally equivalent to this sequence of familiar MIPS instructions (althoughlui is a single instruction) addi Srt, S0, offset s11 Srt, Srt, 16 You should implement lui so that it requires only 3 cycles, and the fetch cycle (state 0) should remain unchanged, (i.e., the instruction word is not available until after this first cycle). Do not modify the existing register file or ALU. Add any necessary components, connections, and control signals to the multicycle datapath (igure available from myCourses, which comes from Ed. 3, Fig. 5.28), and show the necessary modifications to the finite state machine diagram (available from myCourses, which comes from Ed. 3, Fig. 5.38)