Question

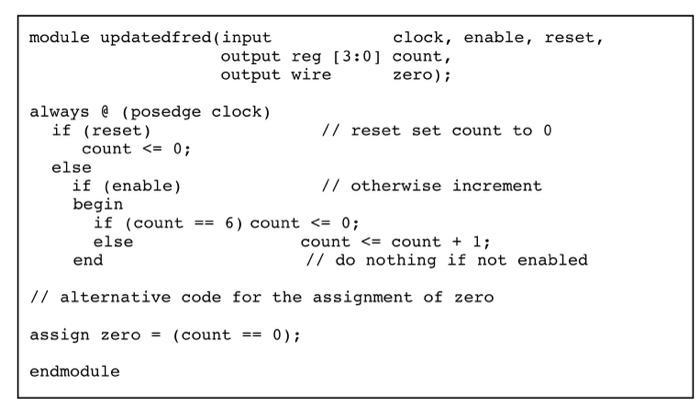

1. Weve added the reset signal as an additional input to the module in the header. However, when will this occur? Will it be synchronous,

1. We’ve added the reset signal as an additional input to the module in the header. However, when will this occur? Will it be synchronous, i.e. synchronised with the clock edge, or will it be asynchronous, i.e. it can happen any time regardless of the value of clock? You have a think.

2. Can you explain what is this code about? Thank you.

3. What is blocking and non-blocking assignment? Whats the difference and their importance?

3. What are the resources to practice on Verilog? Can you also recommend resources for me to practice on hardware designing?

module updatedfred (input clock, enable, reset, output reg [3:0] count, output wire always (posedge clock) if (reset) count

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get StartedRecommended Textbook for

Elements Of Chemical Reaction Engineering

Authors: H. Fogler

6th Edition

013548622X, 978-0135486221

Students also viewed these Programming questions

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

Question

Answered: 1 week ago

View Answer in SolutionInn App