Answered step by step

Verified Expert Solution

Question

1 Approved Answer

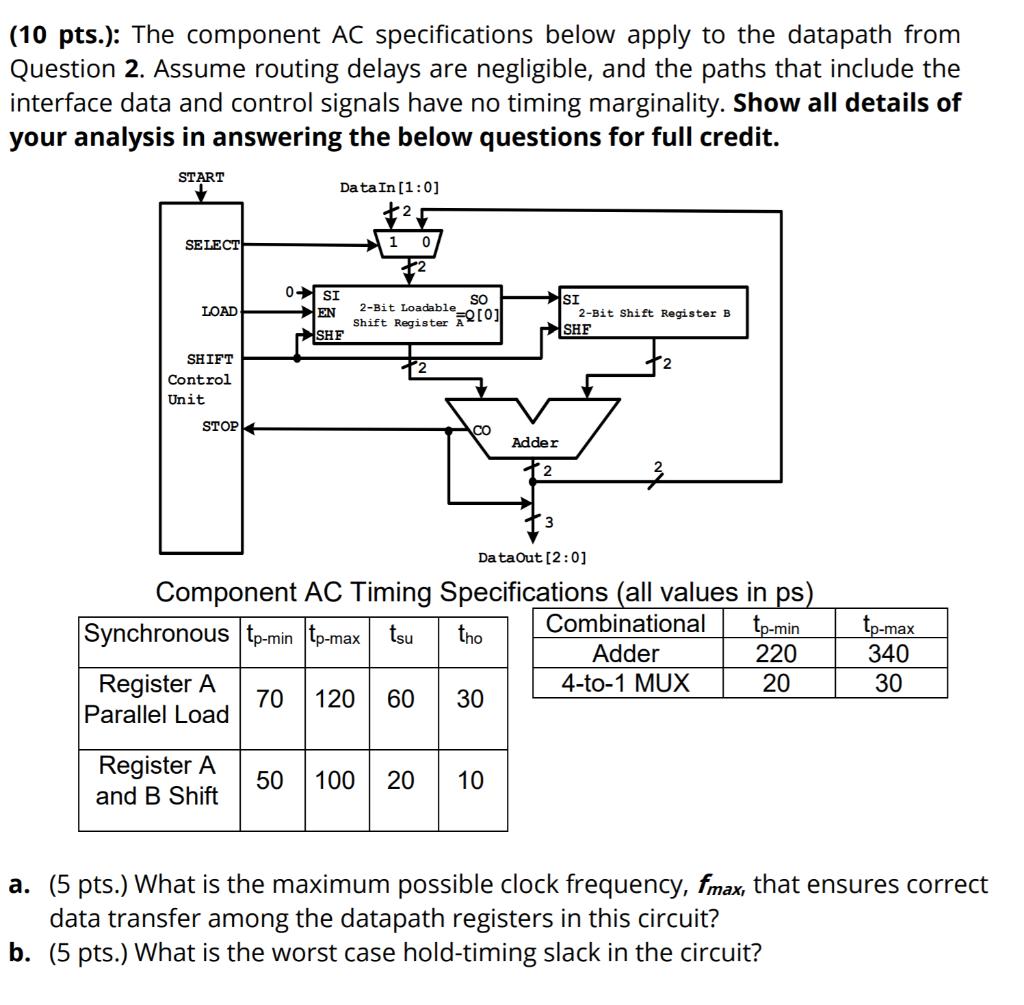

(10 pts.): The component AC specifications below apply to the datapath from Question 2. Assume routing delays are negligible, and the paths that include

(10 pts.): The component AC specifications below apply to the datapath from Question 2. Assume routing delays are negligible, and the paths that include the interface data and control signals have no timing marginality. Show all details of your analysis in answering the below questions for full credit. START SELECT LOAD SHIFT Control Unit STOP Data In [1:0] Register A Parallel Load 0 SI EN SHF Register A and B Shift 2-Bit Loadable SO Shift Register [0] CO Synchronous tp-min tp-max tsu tho 70 120 60 30 Adder 2 DataOut [2:0] Component AC Timing Specifications (all values in ps) Combinational Adder 4-to-1 MUX 50 100 20 10 3 SI SHF 2-Bit Shift Register B tp-min 220 20 tp-max 340 30 a. (5 pts.) What is the maximum possible clock frequency, fmax, that ensures correct data transfer among the datapath registers in this circuit? b. (5 pts.) What is the worst case hold-timing slack in the circuit?

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started