Answered step by step

Verified Expert Solution

Question

1 Approved Answer

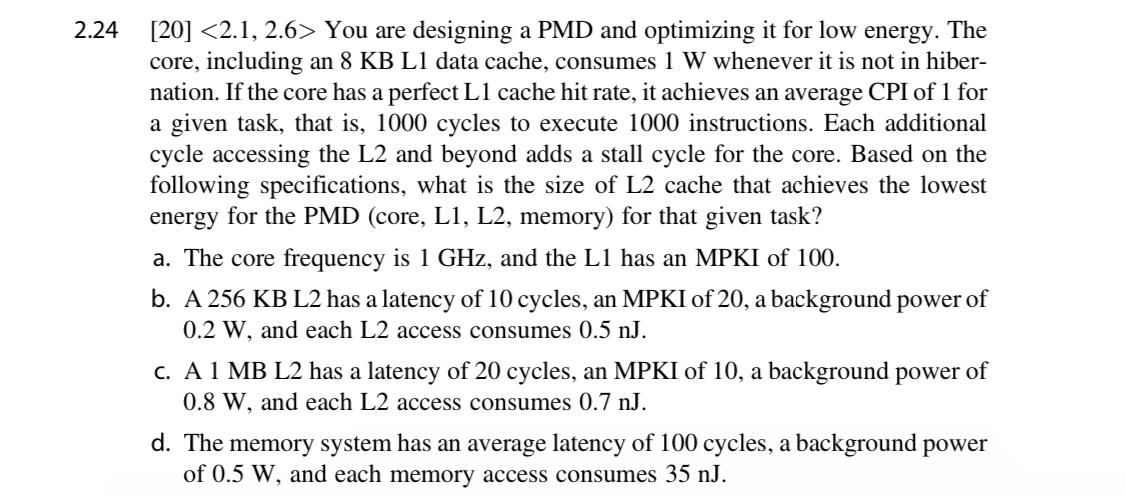

2 . 2 4 [ 2 0 ] 2 . 1 , 2 . 6 > You are designing a PMD and optimizing it for

You are designing a PMD and optimizing it for low energy. The core, including an data cache, consumes whenever it is not in hibernation. If the core has a perfect cache hit rate, it achieves an average CPI of for a given task, that is cycles to execute instructions. Each additional cycle accessing the L and beyond adds a stall cycle for the core. Based on the following specifications, what is the size of L cache that achieves the lowest energy for the PMD core L L memory for that given task?

a The core frequency is and the L has an MPKI of

b A L has a latency of cycles, an MPKI of a background power of and each access consumes

c A MB L has a latency of cycles, an MPKI of a background power of and each access consumes

d The memory system has an average latency of cycles, a background power of and each memory access consumes

Step by Step Solution

There are 3 Steps involved in it

Step: 1

Get Instant Access to Expert-Tailored Solutions

See step-by-step solutions with expert insights and AI powered tools for academic success

Step: 2

Step: 3

Ace Your Homework with AI

Get the answers you need in no time with our AI-driven, step-by-step assistance

Get Started