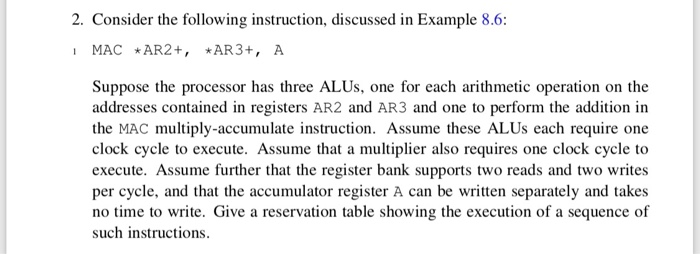

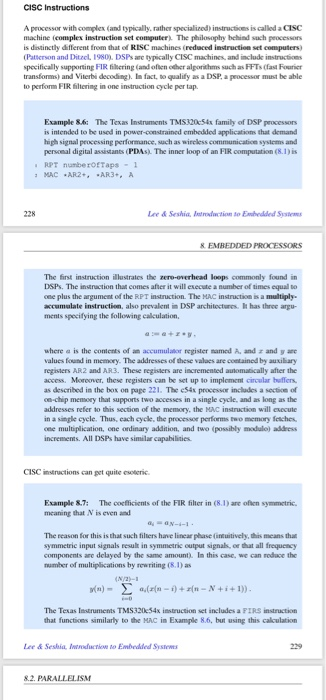

2. Consider the following instruction, discussed in Example 8.6: MAC AR2+, AR3+, A Suppose the processor has three ALUs, one for each arithmetic operation on the addresses contained in registers AR2 and AR3 and one to perform the addition in the MAC multiply-accumulate instruction. Assume these ALUs each require one clock cycle to execute. Assume that a multiplier also requires one clock cycle to execute. Assume further that the register bank supports two reads and two writes per cycle, and that the accumulator register A can be written separately and takes no time to write. Give a reservation table showing the execution of a sequence of such instructions. CISC Instructions A processor with complex (and typically, rather specialized) instructions is called a CIsc machine (eomplex instruction set computer). The philosophy behind sach peocessors is distinctly different from that o RISC machines (reduced instruction set computers) (Patterson and Ditzcl 19809. DSPs c typically CISC machines, and includk instructions specifically supporting FIR filsering (and often other alporithms such as FFTs (fas Fouricr transforms) and Viterbi decodingi. In fact, to qualify as a DSP, a peocessor must be able to perform FIR filtering in one instruction cycle per tap. Example 8.6; The Texas Instruments TMS320C54x family of DSP processors is intended to be used in power-constrained embedded applications that demand high signal peocessing performance, such as wircless communication sysiems and personal digital assistants (PDAsThe inner loop of an FIR computation (8.1) is RPT numbe rOfTaps1 228 Lee & Seshia rodction to Ebedlded Sy 8 EMBEDDED PROCESSORS The first instruction illustrates the zero-overhead loops commonly found in DSPs. The instnaction that comes after it will execute a number of times equal o oee plus the argument of the RPT instruction. The MAC instruction is a multiply accumalate instruction, also prevalent in DSP architoctures. IR has three argu- ments specifying the Sollowing calculation, where a is the contents of an accumulator register mamed A, and z and y arc values found in memoey. The addresses of these valaes are contained by auxiliary AR2 and AR3. These registers are incremented automatically after the access. Moreover, these registers can be set up to implement circular buffers as described in the box on pape 221. The e54s processor includes a section of on-chip memsory that supports two accesses in a single cycle, and as long as the addresses refer to this section of the in a single cyele. Thus, each cycle, the processoe performs two memory fesches oee multiplication, one ordinary addition, and two (possibly modulo) address increments. All DSPs have similar capabilities memory, the MAC instruction will execute CISC instructions can get quite esoteric Example 8.7: The coefficients of the FIR filter in (8.1) are ofien symmetric. meaning that N is even and The reason for this is that such filiers have linear phase (imuitively, this means that symmetric input signals result in symmetric output signals, oe that all frequency components are delayod by the same amount). In this case, we can rodace the number of multiplications by rewriting (8.1) as N/2)-1 The Texas Instruments TMS32054x instruction set includes a FIRS instruction that functions similarly to the MAC in Example 8.6, but using this calculation Lee & SeshiaIrouctioe to Embedded Syste 229 2. Consider the following instruction, discussed in Example 8.6: MAC AR2+, AR3+, A Suppose the processor has three ALUs, one for each arithmetic operation on the addresses contained in registers AR2 and AR3 and one to perform the addition in the MAC multiply-accumulate instruction. Assume these ALUs each require one clock cycle to execute. Assume that a multiplier also requires one clock cycle to execute. Assume further that the register bank supports two reads and two writes per cycle, and that the accumulator register A can be written separately and takes no time to write. Give a reservation table showing the execution of a sequence of such instructions. CISC Instructions A processor with complex (and typically, rather specialized) instructions is called a CIsc machine (eomplex instruction set computer). The philosophy behind sach peocessors is distinctly different from that o RISC machines (reduced instruction set computers) (Patterson and Ditzcl 19809. DSPs c typically CISC machines, and includk instructions specifically supporting FIR filsering (and often other alporithms such as FFTs (fas Fouricr transforms) and Viterbi decodingi. In fact, to qualify as a DSP, a peocessor must be able to perform FIR filtering in one instruction cycle per tap. Example 8.6; The Texas Instruments TMS320C54x family of DSP processors is intended to be used in power-constrained embedded applications that demand high signal peocessing performance, such as wircless communication sysiems and personal digital assistants (PDAsThe inner loop of an FIR computation (8.1) is RPT numbe rOfTaps1 228 Lee & Seshia rodction to Ebedlded Sy 8 EMBEDDED PROCESSORS The first instruction illustrates the zero-overhead loops commonly found in DSPs. The instnaction that comes after it will execute a number of times equal o oee plus the argument of the RPT instruction. The MAC instruction is a multiply accumalate instruction, also prevalent in DSP architoctures. IR has three argu- ments specifying the Sollowing calculation, where a is the contents of an accumulator register mamed A, and z and y arc values found in memoey. The addresses of these valaes are contained by auxiliary AR2 and AR3. These registers are incremented automatically after the access. Moreover, these registers can be set up to implement circular buffers as described in the box on pape 221. The e54s processor includes a section of on-chip memsory that supports two accesses in a single cycle, and as long as the addresses refer to this section of the in a single cyele. Thus, each cycle, the processoe performs two memory fesches oee multiplication, one ordinary addition, and two (possibly modulo) address increments. All DSPs have similar capabilities memory, the MAC instruction will execute CISC instructions can get quite esoteric Example 8.7: The coefficients of the FIR filter in (8.1) are ofien symmetric. meaning that N is even and The reason for this is that such filiers have linear phase (imuitively, this means that symmetric input signals result in symmetric output signals, oe that all frequency components are delayod by the same amount). In this case, we can rodace the number of multiplications by rewriting (8.1) as N/2)-1 The Texas Instruments TMS32054x instruction set includes a FIRS instruction that functions similarly to the MAC in Example 8.6, but using this calculation Lee & SeshiaIrouctioe to Embedded Syste 229